- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a project in which MAX10 has an external ADC that has LVDS connections-- data, ADC_DCO, ADC_FCO.

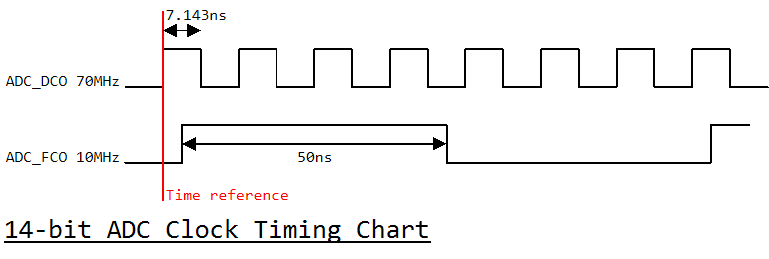

I wrote a constraint for external clocks like the next picture, but Timing Analyzer doesn't recognize the delayed rising edge of ADC_FCO to ADC_DCO.

Both the launch edge and the latch edge rise at the same time. Then Timing Analyzer reports a lack of setup time. Why Timing Analyzer doesn't recognize my phase-shift clock constraint?

My constraint:

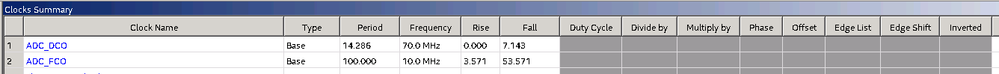

create_clock -name ADC_DCO -period 14.286 -waveform {0 7.143} [get_ports {ADC_DCO ADC_DCO(n)}]

create_clock -name ADC_FCO -period 100 -waveform {3.571 53.571} [get_ports {ADC_FCO ADC_FCO(n)}]

Timing Analyzer read the constraint above.

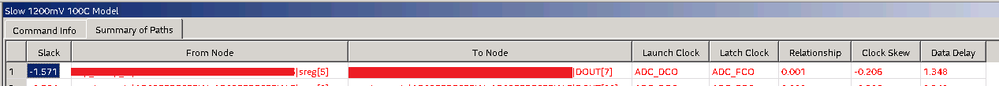

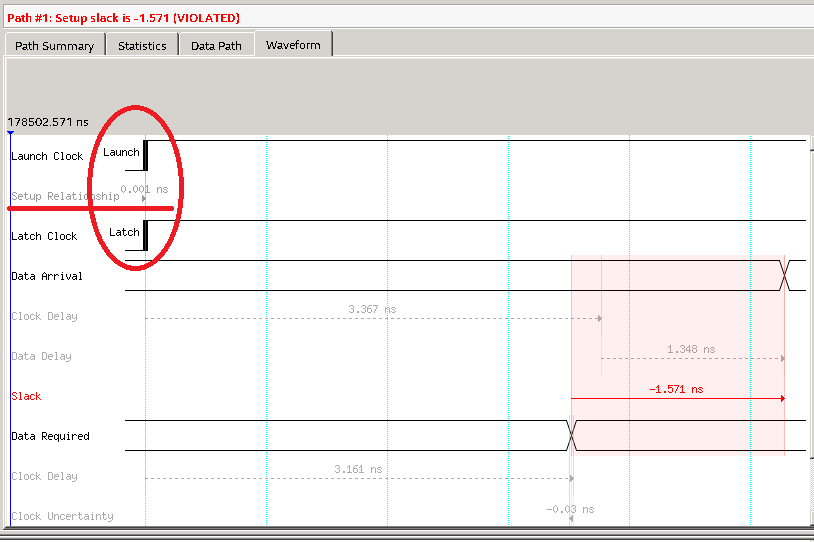

Timing Analyzer reported a setup error.

In the waveform view, the launch edge (ADC_DCO) and the latch edge (ADC_FCO) rise at the sate time. The Setup Relationship is almost 0. Naturally, the setup time is not satisfied. Why the latch edge doesn't delay to the launch edge?

Thanks in advance.

HKana17

My environment

Quartus Prime Lite Edition: 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Windows7 professional sp1

Target device: MAX 10 (10M08)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After looking at the Board Configuration, I believe this is Source-Synchronous Interface.

You may refer to the AN 433: Constraining and Analyzing Source-Synchronous Interfaces, section "Input Clock Constraints" on how to constraint the clock.

With the current clock constraints you have, they are not synchronous with each other. Therefore, meeting either the phase-shift or frequency requirement cannot fulfill both requirements simultaneously.

One approach I can suggest is to write a clock constraint in such a way that Quartus treats this as a PLL, ensuring that both clocks are synchronous with each other.

Regards,

Richard Tan

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After looking at the Board Configuration, I believe this is Source-Synchronous Interface.

You may refer to the AN 433: Constraining and Analyzing Source-Synchronous Interfaces, section "Input Clock Constraints" on how to constraint the clock.

With the current clock constraints you have, they are not synchronous with each other. Therefore, meeting either the phase-shift or frequency requirement cannot fulfill both requirements simultaneously.

One approach I can suggest is to write a clock constraint in such a way that Quartus treats this as a PLL, ensuring that both clocks are synchronous with each other.

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your comments.

I didn't know that kind of configuration name, Source-Synchronous Interfaces.

I see AN433 for the first time. It has many contents, so I would like to take the time to check it.

I will close this case. For another question, I will create a new case.

Thank you again.

HKana17

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

<p>After looking at the Board Configuration, I believe this is Source-Synchronous Interface.</p>

<p>You may refer to the <a href="https://www.intel.com/content/www/us/en/content-details/653688/an-433-constraining-and-analyzing-source-synchronous-interfaces.html">AN 433: Constraining and Analyzing Source-Synchronous Interfaces</a>, section "Input Clock Constraints" on how to constrain the clock.</p>

<p>With the current clock constraints you have, they are not synchronous with each other. Therefore, meeting either the phase-shift or frequency requirement cannot fulfill both requirements simultaneously.</p>

<p>One approach I can suggest is to write a clock constraint in such a way that Quartus treats this as a PLL, ensuring that both clocks are synchronous with each other.</p>

<p>Regards,</p>

<p>Richard Tan</p>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the acknowledgement.

I will transition this thread to community support. If you have any further questions or concerns, please don't hesitate to reach out.

Thank you and have a great day!

Best Regards,

Richard Tan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »