- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have compiled a test design (archive is attached) in order to use the EMIF Toolkit on our external DDR4.

The commands:

Initialize Connections

Link Project to Device

seem to complete without error.

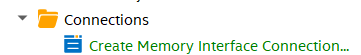

However, when I continue to "Create Memory Interface Connection" (see photo) I am getting an error message "could not establish a connection".

An additional error message appears before that "Calibration was not detected ....".

The project archive and log file is attached.

Any help will be much appreciated.

David

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Please check the "emif_0_status_local_cal_fail" and "emif_0_status_local_cal_success" with signaltap. If none of them toggles please check the ddr4 reference clock. Make sure it becomes stable before the FPGA configuration done.

Regards,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

The DDR4 reference clock was not stable when FPGA entered user mode.

I have fixed this and now the "Create Memory Interface Connection" within EMIF Toolkit does complete OK.

However - there are some remaining issues withe the toolkit and the DDR4 interface.

1.

I have tested W/R to the DDR4 from within the system console.

Up to a certain address (0xF000) the memory seems to work OK - although the number of runs was very small.

From 0xF000 the DDR4 is always reading 0x0.

2.

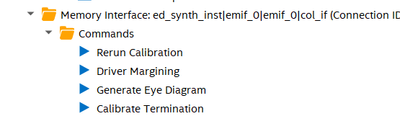

Any action that I try to perform within the toolkit, such as recalibration, or margining, etc, leads to an endless loop within the tool - where I am told to WAIT.

Any help on solving the above two issues would be greatly appreciated.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

For a10 device how do you write and read to the DDR4 from within the system console? I don't think you can control the traffic in this way. The TG module controls the data pattern and customer can't control the TG module. You can change the TEST_DURATION mode for the TG as the guide below:

To do the recalibration, please create Memory Interface Connection first.

After that run the recalibration:

Please refer to the link below for more information on the operation for the Driver Margining:

Regards,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

I will answer your questions in order:

1. Since the EMIF Toolkit was not working, I added a JTAG Master to the QSYS, and temporarily removed the TG from the design.

2. Using EMIF Toolkit, as I stated previously, I am doing all the steps up to, and including, Create Memory Interface Connection.

However, after that point, when I try something like "Rerun Calibration", the Toolkit seems to enter an endless "WAIT" loop.

I am NOT trying to exercise the TG, since I temporarily removed it from the design.

Some more information though:

Using system console, I can see two Masters as seen below:

When I run manual memory tests (just write and read back) from the console I see a few interesting things:

1. Write/Read seem to work OK up to address 0xF000

2. The addresses seem to wrap around at 0x100_0000, 0x200_0000, etc.

Any ideas?

Thanks

David

-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Please generate the ddr4 example design with the guide from the link below:

You can set the memory IO timing with the parameters got from the ddr4 device datasheet and make pin assignments for the custom board. But don't modify the design example, the qsys file can't be changed. Test it after the compilation.

Regards,

Aaron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aaron,

I will try this but it will take some time as I am starting vacation now.

Will be back at work only on 30 April.

So please do not close this thread - I will get back to you eventually.

David

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page