- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have created a project in quartus prime pro 23.4 ant I have used clock control intel FPGA IP as a MUX for clock.And When I run synthesis error encouted.

Error(13224): Verilog HDL or VHDL error at clk_mux_stratix10_clkctrl_2000_yem6tmi.v(67): index 1 is out of range [0:0] for 'clkselect'

And sorry my computer cannot upload any picture

Below is the detail part of clk_mux_stratix10_clkctrl_2000_yem6tmi.v module module

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dupe post.

Answered in your other post that clkselect is single bit but you're using it as 2 bit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, I know what this message means , but this V file is automatically created by QUARTUS prime ,which is why i am confused

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As mentioned above, the input clkselect should be 1bit while you defined it as 2 bit.

Thanks,

Ethan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, I know what this message means , but this Verilog file is automatically created by Quartus prime ,which is why i am confused

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

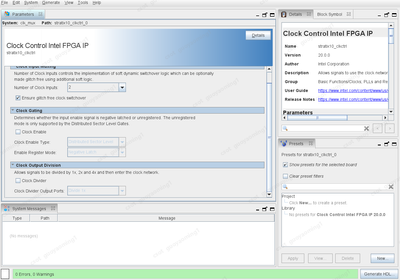

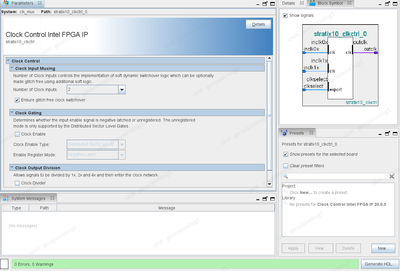

How are you generating this? Is it from the IP? Show your IP parameter editor settings. If it's from an IP, the GUI would prevent you from using illegal values.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So if you regenerate the IP (Generate HDL), you keep getting the same incorrect HDL from the tool?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I do regenerate the IP and only get the same result

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page