- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am currently working on Intel Agilex FPGA (AGFB014R24B2E2V). Quartus Prime pro version 22.2.0 build 94.

I generated my JESD204B example design for Agilex with given presets (LMF = 222). The top file requires two clock as input refclk_xcvr and refclk_core. When I try giving any E tile (9A bank) clock to the refclk_core I get the below mentioned error during fitter stage.

Error(20672): For HSSI E-tile, there is no path between HSSI REFCLK and core. HSSI REFCLK divider "refclk_xcvr~inputFITTER_INSERTED" has core fanouts.

Error(16297): An error has occurred while trying to initialize the plan stage.

Error: Quartus Prime Fitter was unsuccessful. 2 errors, 1 warning

Error: Peak virtual memory: 4662 megabytes

Error: Processing ended: Mon Feb 6 14:19:33 2023

Error: Elapsed time: 00:01:36

Error: System process ID: 19236

Error(21794): Quartus Prime Full Compilation was unsuccessful. 4 errors, 1 warning

Kindly help me in this regard. Also, please clarify why we can not use the same clock for both.

Please let me know if more information required from my side.

Thank you

Regards

Shubhangi

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Thank you for reaching out.

Apologize for the delayed response.

Based on the Agilex OPN number, I believe that you are using Intel Devkit DK-SI-AGF014EA (Prod) type.

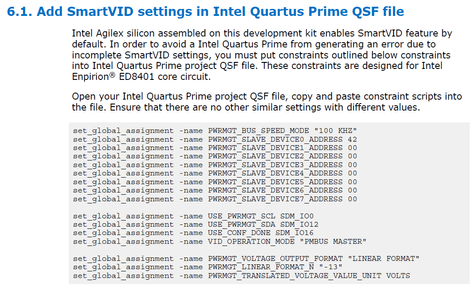

Have you set the VID settings as below?

You are required to input above script/code to avoid Quartus from generating an error due to incomplete SmartVID settings.

You may change the scripts listed below in you project QSF file.

Please ensure that there are no other similar settings with different values.

For more information you may refer to below link:

Hope this helps solve your issue.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Good day.

We do not receive any response from you for more than a week to the previous reply that I have provided.

I wish to follow up with you on this Case.

Have you set the VID settings as my previous reply?

Looking forward to your reply.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shubhangi,

Good day.

We do not receive any response from you to the previous reply that I have provided.

This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page