- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

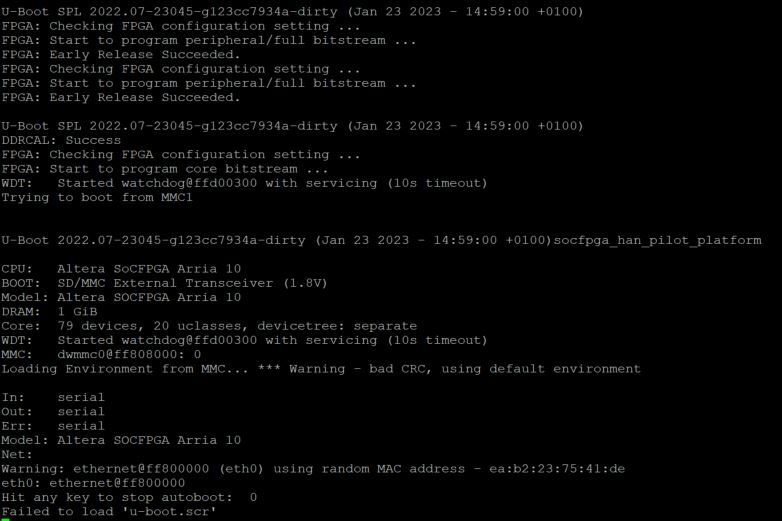

I have adapted the example for the Arria 10 SOCDK (Arria 10 SoC - Boot from SD Card) to the HAN-Pilot-Platform evaluation board from Terasic. I used the make_sdimage_p3.py script to generate the SD-Card image without linux binaries:

Partition 3: (format raw, type 0xA2) - u-boot-splx4.sfp

Partition 1: (format fat) - sdfs folder with - fit_spl_fpga.itb and u-boot.img

Partition 2: (format ext3) - empty

The SOC start-up seems to be ok, but the FPGA does not get configured:

When i start the board without SD-Card, put it in, and then connect with the debugger and start the system with the Debugging U-Boot script. The system boots and the FPGA gets configured…

The start-up runs like from SD-Card, but the FPGA gets configured!

Some more informations:

-

Quartus (22.3 Pro) compilation with “Early Release of HPS IO”

1.1 Qsys EMIF with enabled “Early Release Mode” -

Convert .sof to .rbf with: quartus_cpf.exe --convert --hps -o bitstream_compression=off golden_top.sof golden_top.rbf

-

Make fit_fpga_spl.itb with fit_fpga_spl.its in \u-boot-socfpga\board\altera\arria10-socdk

I recompiled U-Boot with #define DEBUG in include\configs\socfpga_common.h and found these error:

…

No configuration specified, trying default…

Found default configuration: ‘config-1’

FPGA: FPGA node count: 2

FPGA: fpga-periph-1

FPGA: fpga-core-1

FPGA: Start to program core bitstream …

FPGA: Data offset was found.

Can’t get ‘load’ property from FIT 0xffe24ec0, node: offset 248, name fpga-core-1 (FDT_ERR_NOTFOUND)

FPGA: No loadable was found.

FPGA: Using default DDR load address: 0x400 .

FPGA: External data: offset = 0x582d4, size = 0x1dcfb44.

blk_find_device: if_type=6, devnum=0: dwmmc0@ff808000.blk, 6, 0

…

Does anyone have any idea what the problem could be?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @aikeu,

okay, now im sure: The Intel In-System Sources and Probes IP hinders the FPGA from starting normally after it has been correctly configured by SD-Card. Even the old Quartus-Project works without the ISSP-IP. Now it makes sense why the FPGA starts when a connection to the programmer is established via JTAG or similar.

My workaround will be, that i only use FPGA Firmware without the debugging features (ISSP, SignalTap, ...) on the SD-Card and when i need this debugging features i will start the HPS with the ARMD DS debugger.

Thanks for the help, my problem has been solved.

Regards,

LFrin

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @aikeu,

okay, now im sure: The Intel In-System Sources and Probes IP hinders the FPGA from starting normally after it has been correctly configured by SD-Card. Even the old Quartus-Project works without the ISSP-IP. Now it makes sense why the FPGA starts when a connection to the programmer is established via JTAG or similar.

My workaround will be, that i only use FPGA Firmware without the debugging features (ISSP, SignalTap, ...) on the SD-Card and when i need this debugging features i will start the HPS with the ARMD DS debugger.

Thanks for the help, my problem has been solved.

Regards,

LFrin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi LFrin,

Glad that the issue has been resolved and thanks for sharing with the workaround method through your troubleshooting process.

I will close this thread for now and do consider open a new thread when there is further question.

Thanks agian.

Regards,

Aik Eu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »