- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I am working in a bring-up of a board that contains a Cyclone 10 LP FPGA.

I am trying to use the 2x PLLs that the FPGA contains.

I have generated from the 100MHz input clock, 2x 200KHz using ALTPLL IP.

But, I see that the "locked" out signal goes from "1" to "0" after programming the sof and that the output frequency us around 170KHz instead of the 200KHz.

I have tried different compesation modes and made tests with different frequencies, but I always get the same behavior, "locked" signal does not get stable in "1" and the PLL output frequency is always below the target (i.e. 15MHz I get 12MHz, 5MHz I get 4Mhz, ...)

I am unsure if it's IP config problem or something else, like HW isuse.

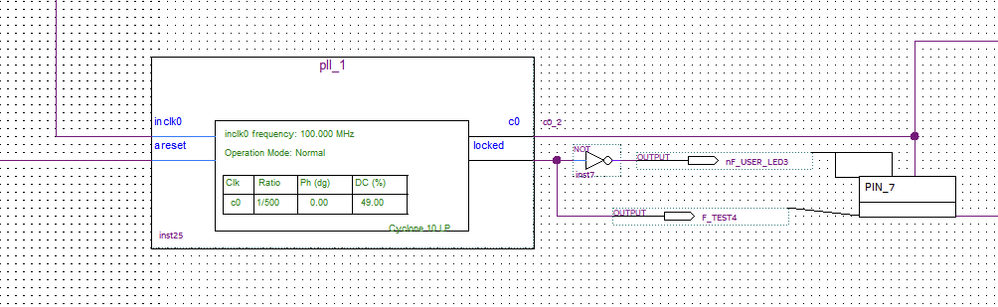

A small capture of the IP:

How can I proceed?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can confirm that the input clokc is working fine, as I have used it to toggle LEDs using a counter module.

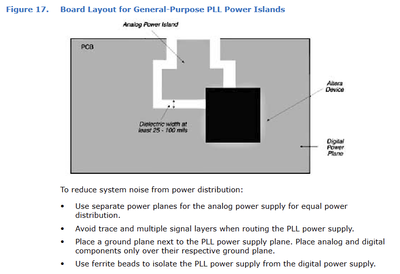

I am wondering if it is mandatory to have an isolated analog reference plane in the PCB as stated in doc an958:

In my design, we only have a ferrite to isolate VCC_PLL but we have not created an isolated GNDA, it is tied to digital ground.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Power integrity is hardly a problem unless your PCB has many fast switching outputs.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, the board has VCC_PLL decoupling caps, but is also missing a ferrite bead for VCCA feeding voltage.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May I know if you confirm the 100MHz input clock is stable through waveform measurement? Another thing to highlight here is the power supply for analog, VCCA. Does it confirm supplying the stable power? The VCC must rise monotonically.

Refer to the datasheet for the VCCA recommended operating condition:

Regards,

Aqid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It looks to be a hw, the "GNDA" pins are missing GND connection

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay noted. Has the issue been resolved after you are connecting the GNDA pins to GND?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, issue solved

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page