- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to use SLD hub in MAX-V FPGA.

The sink of SLD hub would be SLD node in the FPGA fabric.

How about the source of SLD hub ? , what is it's input ? (channel and protocol).

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

sld_hub_controller is used as lower level interface in sld_hub_controller_system and jtag-over-protocol IP, which are the hardware interfaces of documented remote debug solutions, see AN693 and AN971. The interfaces and protocols are not documented as such.

altera_streaming_sld_hub_controller_core.sv source has however meaningful comments, variable and state names, it's not too difficult to understand the intended usage. A testbench can help to figure out control timing.

MAX V has limited debugging capabilities due to low LE count, which debugging functions are you looking for?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

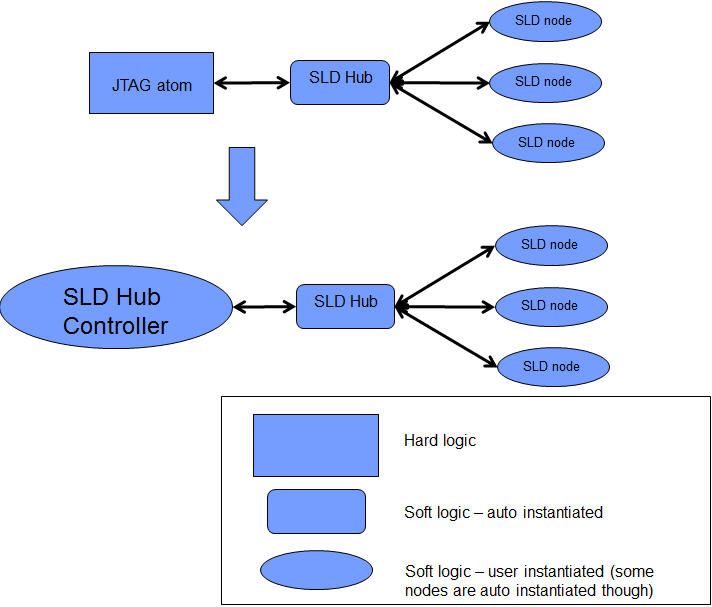

You may refer to this diagram :

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Farabi,

I have look the diagram.

Its from AN 693: Remote Hardware Debugging over TCP/IP for Altera SoC.

How the SoC can be replaced with the FPGA to debug over TCP/IP.

I want to debug the MAX-V FPGA.

thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There's a principle option to implement hardware TCP/IP stack in FPGA (probably needing more logic cells than provided by MAX V), but it's not supported by any Intel IP.

A processor-less remote debug interface can be easier implemented through other fast serial links.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Frank,

I can replace MAX V with MAX10.

*************

There's a principle option to implement hardware TCP/IP stack in FPGA (probably needing more logic cells than provided by MAX V), but it's not supported by any Intel IP.

I have planned this initially but dropped due to complexity.

*************

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am sorry for late reply. You may want to explore remote debugging setup from this link : https://www.intel.com/content/www/us/en/support/programmable/articles/000078790.html

By enabling JTAG over network, you can use all the Quartus features including signaltap from remote.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Do you have further request?

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided, please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page