- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The following reference design is based on 1SM21BH device.

https://fpgacloud.intel.com/devstore/platform/19.1.0/Pro/an881-pcie-avmm-dma-gen3x16-ddr4-and-hbm2/

We use Stratix 10 MX 1SM21CH device, so we cannot synthesize this reference design.

I guess the difference is HBM controller interface because of the size.

Could you please provide a version for 1SM21CH device?

This reference is important to us, or we don't know how to access HBM2/DDR4 by PCIe driver.

Thanks.

Link Copied

- « Previous

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

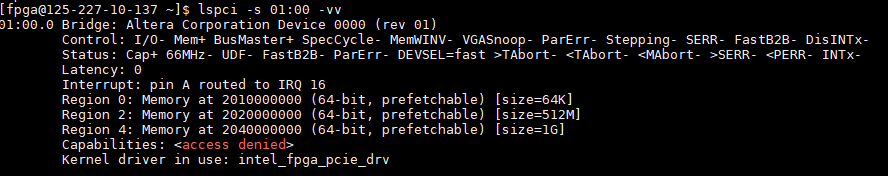

After we enabled BIOS "above 4G decoding" setting, the BAR address and memory space could be allocated.

Besides, we modified PCIe class code from default 0xff0000 to 0x068000 (Bridge device).

Otherwise BIOS of our motherboard doesn't allocate BAR of FPGA.

It seems you don't have this class code issue.

But capabilities are still "access denied".

Would it be a problem? Or it's normal?

And then, we can change BAR number after above modification,

but link test and DMA functions still fail.

All the read value of link test is 0xffffffff, which is error code replied by system.

Is your situation the same?

Besides, the test program shows " Stopping DMA run due to error." when we trigger DMA function.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I review the thread today again and found this post. I think this is nearer to the approach. The access denied should be due to your log in do not have admin access. try to type a command like sudo <password>.

Also, you need to load the driver.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

By the way, please contact the design author as soon as possible to see what's wrong.

We have to make our deadline, because there will be a demo of our design to customers in the end of December.

This FPGA board has been bought for almost 2 months.

However, no reference design works so far.

https://fpgacloud.intel.com/devstore/platform/?acds_version=any&family=stratix-10&board=104

We assumed that at least one of above reference designs could prove this board's function is normal.

But the simplest "on-chip memory reference design" cannot be installed. (I've asked another question about this issue on community)

And the other three reference designs cannot work.

If there is no way to prove the functionalities of this FPGA kit,

maybe we need to return it to Intel.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

I am still waiting for response from the author. Sorry for the delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

We did a lot of experiments, e.g. to reduce the required BAR space, to rule out BIOS issues, motherboard issues, and Linux OS issues.

Yesterday we find a reference design from Terasic, that design uses "PCIe hard IP hen3x8", and it works on our platform.

But the reference design is only PCIe and on-chip SRAM.

We still need a whole system like AN881 with HBM2.

Therefore, we strongly doubt that the root cause is some bugs in PCIe hard IP+ gen3x16 (Quartus V19.3).

Please help to forward the information to design author, and fix the issue of AN881 reference design.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sir, do you have chance to run the TCL as mentioned in my previous comment?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, we are trying.

I'll reply to you after the experiment done.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi I noticed that in the reference design, there are script.zip, and one of the file is update_qsys_generated_files.tcl

Please update the parameters as below based on your current project

set PROJ_ROOTDIR "path of your project"

set QSYS_SYSTEM g3x16_hbm2_ddr4

set QUARTUS_VERSION 193

and then run the tcl and recompile the design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We just finished the experiment.

The result is still the same after we use the script.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

I am very sorry for the inconvenience caused.

When I discovered the tcl file, the MX board already pass to others. So, I don’t have chance to verify it by myself. And in timely manner, I give you the steps and try it at your side with the hope to get a positive result. I need some time to get the board back.

And today, I just received the latest design from the author, he claimed that this design is verified work at his side. I checked this design still using E2 which I believe he is using some prototype board that using E2 device. Thus, I change it to E1, regenerate the qsys and run the TCL. I am then compiling the design. So, I just pass the SOF to you. If you available, please help to give it a try with this SOF. Otherwise, I will queue to get the board and test it on my side.

From this latest design, I can see the BAR setting is turned on for BAR2 and BAR4 which I believe it’s more reliable.

I also attach the design QAR for your reference. This design is using 19.2. Anyway, you do not need to install 19.2 as for now. You can use 19.3 programmer to program the SOF and test it directly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have tested this with sof.

It still doesn’t work at our side.

Could the author provide the environment information like motherboard name, Linux version, and Quartus version? And try the the device exact the same with ours?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi author is using using an AMD GEN4 Workstation with Ubuntu version. He generated the SOF with 19.2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

OK.

We also tried Ubuntu and Quartus 19.2.

So it seems not an environment issue.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

- Next »