- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm a beginner who has just started working with SOC_FPGA. I'm using two DE10-nano boards and I want to generate video color bars on one board and then transfer them to the another board through Ethernet, and finally display them through HDMI.

However, after generating the data on the FPGA side of the first board, I don't know how to use Ethernet to transmit it to the second board. Can someone give me some idea of the general approach?

Thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You need to transfer data from FPGA to HPS DDR memory using the DMA or FIFO and the F2H bridge. This will be in your Verilog code.

In software linux, you need to write the linux userspace code for reading data from DDR and fill the buffer and send over HPS ethernet.

For ethernet in linux you need to write the socket programming to build the TCP/IP or UDP application over ethernet for server or client on board.

We don't have this example code but it is generic way of writing the linux TCP/IP app. For reference you can refer below link

https://www.geeksforgeeks.org/tcp-server-client-implementation-in-c/

For HPS & FPGA data transfer, please refer the below link.

https://github.com/robertofem/CycloneVSoC-examples/tree/master/Linux-modules/DMA_PL330_LKM_basic

Let me know if you have any other query on this topic.

Regards

Tiwari

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In linux, you need to use the socket programming for ethernet data sending or receiving. With this you can send/receive data using the raw data or with TCP/UDP protocol.

Regards

Tiwari

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I believe your enquiry has been answered. With that, I now transition this thread to community support.

Thank you.

Best Regards,

Tiwari

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your help. I want to use FIFO to receive data from FPGA, then use Avalon MM Pipeline Bridge to send the data to F2H AXI bus, and then write a program on Linux to read and send the data. I don't know if this is okay

- Tags:

- F2H AXI bus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You need to transfer data from FPGA to HPS DDR memory using the DMA or FIFO and the F2H bridge. This will be in your Verilog code.

In software linux, you need to write the linux userspace code for reading data from DDR and fill the buffer and send over HPS ethernet.

For ethernet in linux you need to write the socket programming to build the TCP/IP or UDP application over ethernet for server or client on board.

We don't have this example code but it is generic way of writing the linux TCP/IP app. For reference you can refer below link

https://www.geeksforgeeks.org/tcp-server-client-implementation-in-c/

For HPS & FPGA data transfer, please refer the below link.

https://github.com/robertofem/CycloneVSoC-examples/tree/master/Linux-modules/DMA_PL330_LKM_basic

Let me know if you have any other query on this topic.

Regards

Tiwari

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

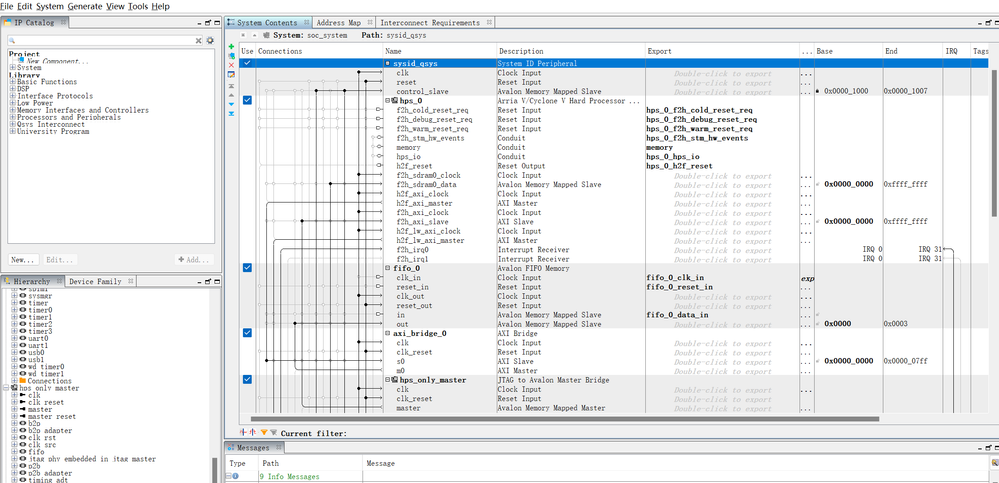

I am using FIFO and AXI Bridge, where s0 of AXI Bridge is connected to H2F AXI Master, and m0 is connected to the output of FIFO as shown in the figure. Since AXI Bridge s0 is in Avalon-MM Slave mode, it cannot be connected to F2H AXI Slave, so I can only connect it to H2F AXI Master. If I connect it as shown in the picture, will it still be possible to read data correctly from the HPS side?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Avalon and AXI memory-mapped interfaces can be connected to each other but the streaming versions cannot be used (and you can't connect Avalon streaming to AXI streaming either).

Regards

Tiwari

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I believe your enquiry has been answered. With that, I now transition this thread to community support.

Thank you.

Best Regards,

Tiwari

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This task is too difficult for beginners. I like to start with smaller goals first. Now I have generated some 32-bit data on the FPGA side, can I connect it as shown in the above picture, and use the mmap function on the Linux side to access these data?

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page