- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear team,

I would like to thank Intel for providing us with the expensive software and hardware through devcloud. I am grateful.

I am using devcloud for my graduate research program in the University, which is based on DPC++ for FPGAs.

Compiler version discrepancies in different nodes

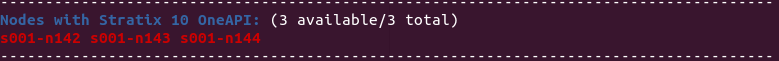

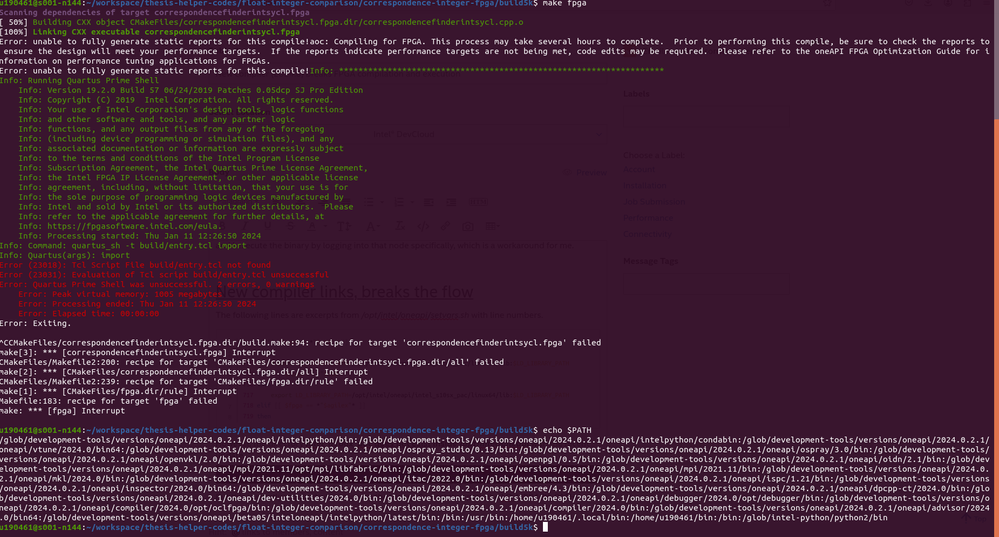

I realized that for both compilation and execution of DPC++ programs, one of the Nodes with Stratix 10 OneAPI has to be used as shown below.

When the environment variables are sourced in the nodes using the following command,

source /opt/intel/oneapi/setvars.sh

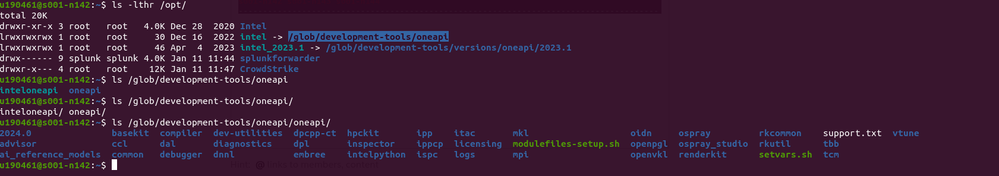

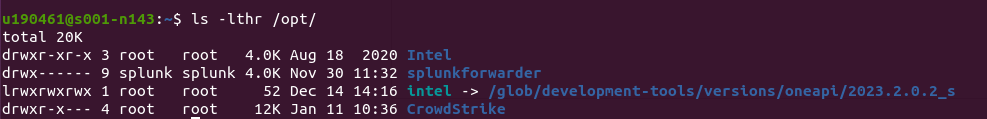

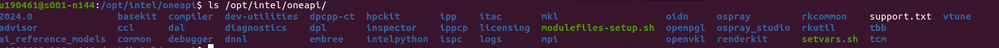

different environment variables are presumably set because /opt/intel/ refer to different files in different nodes.

So, as a workaround, I made it a practice to compile DPC++ programs for FPGA by defining the node name. For example,

qsub -l nodes=s001-n142:ppn=2 -d . ~/integer_correspondence_compile_10k

and I execute the binary by logging into that node specifically, which is a workaround for me.

New compiler links, breaks the flow

The following lines are excerpts from /opt/intel/oneapi/setvars.sh with line numbers.

712 if [[ $fpga == *"$a10"* ]]

713 then

714 export LD_LIBRARY_PATH=/opt/intel/oneapi/intel_a10gx_pac/linux64/lib:$LD_LIBRARY_PATH

715 elif [[ $fpga == *"$s10"* ]]

716 then

717 export LD_LIBRARY_PATH=/opt/intel/oneapi/intel_s10sx_pac/linux64/lib:$LD_LIBRARY_PATH

718 elif [[ $fpga == *"$agilex"* ]]

719 then

However, the directory intel_a10gx_pac does not exist inside /opt/intel/oneapi with the recent update.

But this is mostly required when running the binary file.

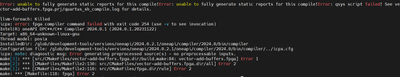

Now, I am not even able to synthesize in the first place.

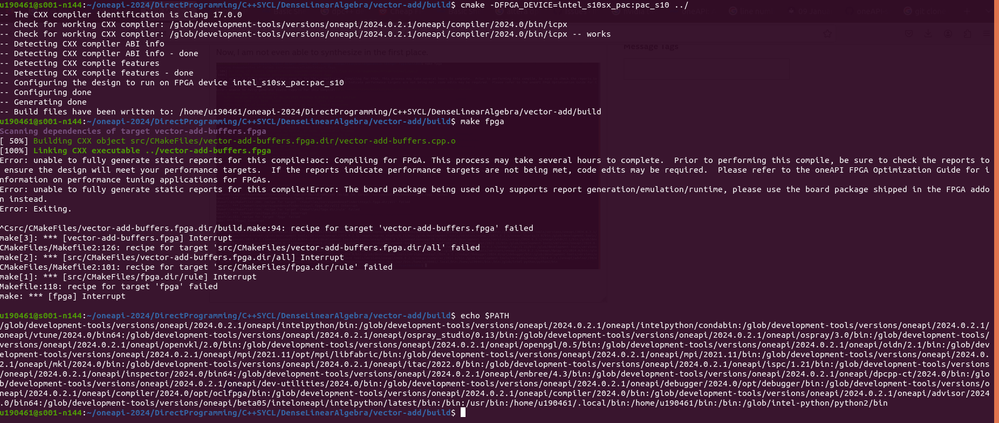

Here is an attempt to compile the vector-add program from oneAPI-samples git repo

Am I doing something wrong or is it a bug with the new update?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have the same problem. It seems there is a problem with the pac_a10 and pac_s10 BSPs.

To reproduce using the oneAPI-samples git repo (https://github.com/oneapi-src/oneAPI-samples/tree/master/DirectProgramming/C%2B%2BSYCL_FPGA/Tutorials/GettingStarted/fpga_compile)

cd oneAPI-samples/DirectProgramming/C++SYCL_FPGA/Tutorials/GettingStarted/fpga_compile/part4_dpcpp_lambda_buffers

cmake .. -DFPGA_DEVICE=intel_a10gx_pac:pac_a10

# Error: The board package being used only supports report generation/emulation/runtime, please use the board package shipped in the FPGA addon instead.

Compiling for the Arria10 device family works, but then the binary cannot be run on the pac_a10 board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for posting in Intel communities.

Sorry for the delay.

Thank you for sharing your observations with us, we were able to reproduce the issues from our end and we are working on them internally.

FPGA emulations are working fine on Stratix10 and Agilex nodes.

Thanks,

Jaideep

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay, but we are still working on this issue and will get back to you with an update.

Thanks,

Jaideep

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @JaideepK_Intel for letting me know about the progress. I totally understand that Intel has no obligation to fix it soon and I am grateful for the fact that it is providing us with the features available to us. One of the crucial parts of my research are the results from actual FPGA boards which makes the research sound, rather than the emulation or simulation. We are working on an academic publication paper and we will include our gratitude to Intel in the same. I hope to see the issue fixed which lets us run our application on the FPGA board. Thanks, I appreciate the help. Cheers

Regards,

Roche Christopher

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page