- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are under the design of the power stage of a FPGA system.

We would like to use the EN2342QI as a midbus converter.

The system will have 12V input that will power the EN2342QI. The EN2342QI will generate 5V and from this 5V different ICs will generate the remaining power rails of the system (1V, 1.5V, 1.8V, 3.3V).

The EN2342QI will work as single input supply.

I have several questions in order to be sure that the design will work:

1. We will have nearly the maximum allowed output bulk capacitor in the 5V bus (~120uF). I would like to know if increasing the SS time (from 47nF, 3.2ms to 220nF, ~15ms) will allow the EN2342QI to be able to drive >120uF. Or if the high SS time will be a drawback (if this trigger any internal protection). We don't need a quick start up.

2. For external loop compensation and Ra and Rb selecction, shall we use the Table 4 recomended values or que once listed at Table 6? What are the proper values for 12V input, 5V output and 110uF-120uF (with 15ms SS if this is ok)?

3. For trigger the enable of the EN2342QI we will use a resistor divider from the 12V input. We have taken into account the internal Pulldown resistor of the EN2342QI, we would like to know if this is OK with the minimum slew rate of Enable signal. The EN2342QI won't be turned on/off during operation, It will be ENABLED once the system is powered and work all the time the system is powered. Shall we consider the ENABLE Lockout Time? Or this is only the minimum off-time before re-enable?

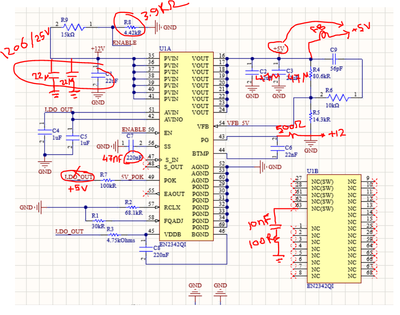

Please have attached a picture of the design of the EN2342QI. I would like to know if you can validate the design.

Thanks in advance.

Juanjo

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Juanjo ,

I have reviewed your schematic and your below questions and have updated the schematic to satisfy your requests.

But i would recommend, if the only use for the 5V rail is to be intermediate bus, is to reduce EN2342 output to be 3.3V and use it to power your 3.3V rail and in same time use the 3.3V as an intermediate bus for the rest of the rails.

Also the other solution is to use EC2650 (6Vout) which much efficient than EN2342 and also will have smaller solution size which will reduce the cost too.

Thanks,

Mostafa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the feedback.

We need to keep the EN2342QI with 5V output in order to be able to power downstream electronics.

So we would like to keep the 5V output for the EN2342QI.

Regarding the output capacitors, I see you place 2x47uF and then the ferrite bead. Can we place more bulk capacitors after the ferrite? I ment the output bulk capacitance will be 94uF then the ferrite bead, but after this, there are all the input bulk capacitors for the rest of the DC/DC capacitors (at least 14.7uF for each converter) making a total of nearly ,160uF. Will the ferrite bead will be enough for decoupling the capacitance?

Cant we increase the SS capacitance in order to decrease the inrush current ?

Thanks for the support.

Best regards,

Juanjo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Juanjo,

I increased the output caps to 2x47uF where there is a high capacitance de-rating at 5V bias.

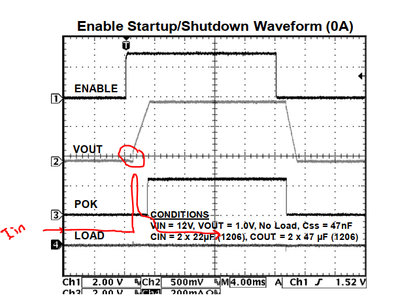

The need for the FB is to limit the inrush current during the startup, unfortunately increasing the Css (>47nF) value will not help a lot where most of the inrush caused by the first voltage step which has a very high slew rate as shown below

So please don't increase the Css more than 47nF.

There is no issue with the input capacitors of the downstream regulators since that capacitators located after the FB which will limit the inrush current.

Thanks,

Mostafa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mustafa,

Thanks for the feedback.

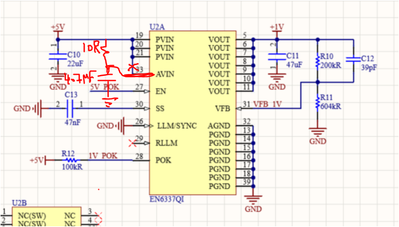

I have modified the Schematic, please find attached a capture of the hole power rails design. The FB10 is a 30Ω @ 100MHz, 25%, 0.01Ω, 5A.

All the DC/DC are from intel (EN6337QI, EN2342QI and 3x EP53F8QI) , I would like to know if you can validate design of all the power rails.

If it is not please, validate the part of the EN2342QI and I will open a new post.

Thanks in advance,

Best regards,

Juanjo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Juanjo,

I am sorry for late response, i already did the review for the downstream regulators last time but unfortunately forget to write my below feedback.

The circuit design for all the downstream regulators are okay, only i would recommend to insert an RC filter for EN6337_AVIN signal as shown below, this to reduce the noise on the AVIN and avoid triggering the UVLO many times if there is any noise on the 5V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mostafa,

Thanks for your feedback.

I would like to know if you can share with me you mail. I would like to know the ripple of the EN2342QI when operating at 12V as input and 5V as output.

Might be a better solution to use the EN2342 to generate 3.3V as you proposed and use other IC for generating the 5V rail bus if the output of the EN2342QI will be quite noisy.

Thanks in advance,

Juanjo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mostafa,

can you please share Voltage ripple of the output of the EN2342QI for Vin= 12V, Vout=5V and loaded with ~2A?

This will clarify if we shall continue with the designed stage or change the design.

Thanks in advance,

Juanjo

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page