- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have installed OneAPI and Quartus pro23.3 on Ubuntu 22.04LTS, and I have download oneAPI-samples from github.

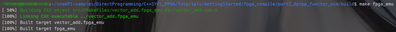

According to the tutorial, I cd the directory "oneAPI-samples/DirectProgramming/C++SYCL_FPGA/Tutorials/GettingStarted/fpga_compile/part2_dpcpp_functor_usm", then

source /opt/intel/oneapi/setvars.sh

export PATH=$PATH:[the path of quartus]

mkdir build && cd build

cmake ..

When I make fpga_emu and run vector_add.fpga_emu, There is no problem.

But when I run vector_add.fpga_sim or vector_add.fpga, the following error has occured:

I don't know how to solve this problem, and I hope to get your help.

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi longgnol,

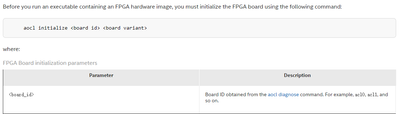

I think you will need to run through board initialization first.

Can refer to the related steps as below:

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply.

The document says that Board ID obtained from the aocl diagnose command.

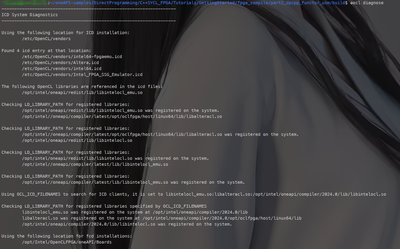

I run aocl diagnose command, and I get the following result:

Is the error because I am missing any software packages?

My card is Agilex DK-DEV-AGI027RES.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi longgnol,

I think you will need to go through the IP authoring flow for your Agilex device.

Refer to the links below:

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi aikeu,

Can IP authoring flow meet these requirements?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi longgnol,

Yes, you can write the code that can interact between FPGA and CPU in IP Authoring.

IPA flow have more library that oneAPI created for algebra related use case

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi aikeu,

Does this card Agilex DK-DEV-AGI027RES have a corresponding BSP?

And where am I going to download its BSP? I couldn't find the download link on the official website.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi longgnol,

For IP authoring, it will not require BSP for Agilex. Only S10 and A10 need the BSP.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi longgnol,

I am closing the thread for now as we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

Thanks.

Regards,

Aik Eu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page