- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

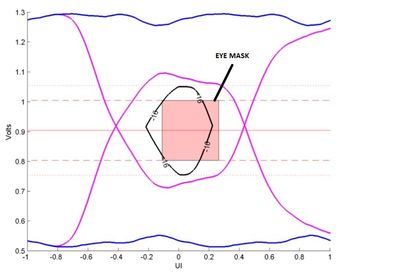

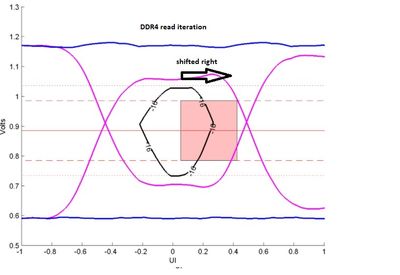

We are trying to run DDR4 read simulation using MBERE 1.25 tool using C3000 family spice deck. I am trying to understand how the eye mask is calculated in the tool?

Can we modify the eye mask by changing some parameter?

During read iteration I see the mask has shifted right with change in corner values. Is this is valid? Please find the attached snapshot for the reference.

Could anyone please support us understanding the above.

Regards,

Shashi S

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S:

Thank you for contacting Intel Embedded Community.

You should review the information stated in section 2.2, on pages 3 and 4 of the Intel® Memory Bit Error Rate Executable (Intel® MBERE) User’s Guide document # 569813. You can find it when you are logged into your Resource & Design Center (RDC) privileged account on the following website:

https://cdrdv2.intel.com/v1/dl/getContent/569813

You should fill out the RDC Account Support form to process your account update request or report any inconveniences with the provided site. You can be found on the following website:

https://www.intel.com/content/www/us/en/forms/support/my-intel-sign-on-support.html

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @CarlosAM_INTEL,

Thanks for the response.

The document "Intel® Memory Bit Error Rate Executable (Intel® MBERE) User’s Guide document # 569813" and section 2.2 you were referring doesn't contain any information about eye mask.

Could you please re-check? I kindly request your support on this to help us understand the MBERE tool.

Regards,

Shashi S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S:

Thanks for your reply.

We want to address the following questions to better understand this situation:

Could you please let us know the part number of the processors related to this situation?

Could you please inform us if this situation happens with the cited version of the tool or others?

Could you please clarify if the affected design has been developed by you or others?

We are waiting for your answer.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @CarlosAM_INTEL ,

Please find my response inline below.

Could you please let us know the part number of the processors related to this situation?

> We are using C3000 series C3558 and C3338 device

Could you please inform us if this situation happens with the cited version of the tool or others?

> Yes, this situation is happening with cited version of the tool, i.e. MBERE 1.25

Could you please clarify if the affected design has been developed by you or others?

> Yes, the affected design is developed by me.

I hope above response provides the required clarification. Please let me know if more details required.

Regards,

Shashi S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S:

Thanks for your reply.

You should use version 1.4 of the cited tool document # 554422 to reproduce the reported condition and let us know if the situation persists. You can find it when you are logged into your Resource & Design Center (RDC) privileged account on the following website:

https://cdrdv2.intel.com/v1/dl/getContent/554422

You should fill out the RDC Account Support form to process your account update request or report any inconveniences with the provided site. You can be found on the following website:

https://www.intel.com/content/www/us/en/forms/support/my-intel-sign-on-support.html

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much for the clarification provided.

I am able to run the ddr4 data .tr0 with the MBERE 1.4 tool.

Does MBERE 1.4 version works for Command and address bus .tr0 too, or it is only upgraded to support data .tr0?

When I compare the results of both tool version, it is observed that result is compared against the spec value mentioned in the tool report i.e. TDIPW = 281.25ps and VIHLAC = 0.12V. While actual DDR4 JEDEC spec specifies TDIPW = 310ps, VIHLAC = 186mV @ 1866MTs. Could you please provide some clarification on this deviation?

Regards,

Shashi S

- Tags:

- Hi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S:

Thanks for your reply.

We want to have more information on the design related to the reported situation to give proper information to answer your questions.

Could you please list the sources that you have used to develop the affected design?

Could you please confirm if the affected project has been verified by Intel?

Thanks in advance for your answer to these questions.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @CarlosAM_INTEL ,

Please find the clarification below.

I am using the spice deck available for C3000 in the following link

Intel Atom Processor C3000 Product Family DDR4 HSPICE Signal Integrity Model User Guide [MUG]

Using 2G6E1 DDR4 Micron memory UDIMM @2333MTs.

And my layout platform, which is not yet reviewed by Intel, but it is expected to happen shortly.

I hope above details provide required clarification.

Regards,

Shashi S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S:

Thanks for your reply.

However, it seems that you do not understand my first question, please let me paraphrase it.

Could you please list the Intel documents that you used to design the implementation reported as affected by this condition? (such as schematics, design guides, datasheet, specification updates, thermal-mechanical design guides, or other documents)

On the other hand, you can send your schematics and layout implementations to be verified by Intel using the procedure stated on the following website:

https://edc.intel.com/Tools/Design-Review/Default.aspx

We are waiting for your answer.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @CarlosAM_INTEL ,

Please find the details of the documents referred for design and simulation. Please note that, currently I am working on point-to-point DDR4 UDIMM interface.

Design:

558578:Intel Atom® Processor C3000 Product Family Platform Design Guide (PDG) Revision: 2.7

Intel Atom® Processor C3000 Product Family Datasheet

558800-c3000-ddr4-tlc-rev1p3.xlsm

Simulation:

Intel Atom Processor C3000 Product Family DDR4 HSPICE Signal Integrity Model User Guide [MUG]

569813-569813-mbere-users-guide-rev1-01.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S:

Thanks for your update.

You should review the information stated on pages 24 through 35 of the DDR4 SI Overview Harrisonville Example document # 563963 related to the MBERE tool. You can find it when you are logged into your Resource & Design Center (RDC) privileged account on the following website:

https://cdrdv2.intel.com/v1/dl/getContent/563963

You should fill out the RDC Account Support form to process your account update request or report any inconveniences with the provided site. You can be found on the following website:

https://www.intel.com/content/www/us/en/forms/support/my-intel-sign-on-support.html

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @CarlosAM_INTEL ,

Thank you for providing the reference.

I have been through the schematics and layout review service page by Intel in the below link.

Design Review Services (intel.com)

Could you please help us in reviewing our spice deck which we have modified, so that we can make sure that our approach is in right direction.

Regards,

Shashi S

- Tags:

- Hi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @Shashi_S

Thanks for your reply.

You should use the Intel Atom Processor C3000 Product Family DDR4 HSPICE Signal Integrity Model User Guide [MUG] document # 557297. You can find it when you are logged into your Resource & Design Center (RDC) privileged account on the following website:

https://cdrdv2.intel.com/v1/dl/getContent/557297

You should fill out the RDC Account Support form to process your account update request or report any inconveniences with the provided site. You can be found on the following website:

https://www.intel.com/content/www/us/en/forms/support/my-intel-sign-on-support.html

Best regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page