- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

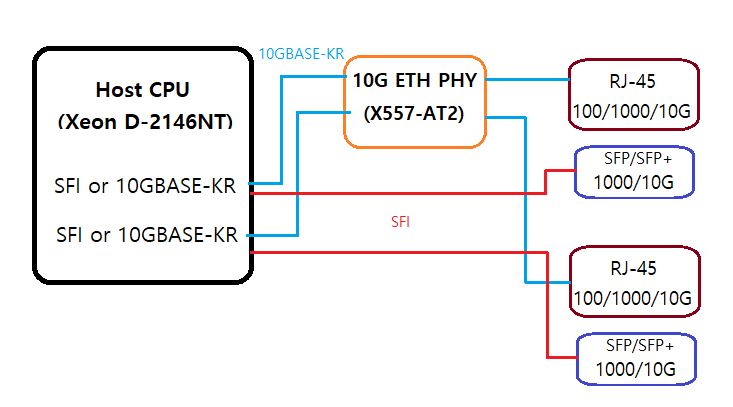

But, for supporting multiple interface, such as 100/1000/10G, I needed to use ethernet phy like X557-AT2.

Therefore in this time, my question come up.

if I have only two networking port, can I connect the 10GBASE-KR interface to the chip-set, and the SFI interfaces are connected to the SFP cage? simultaneously?(see the above diagram plz)

let me know.

Thanks in advance.

Joe

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ZShin,

Thank you for joining the Intel community

I will route your question to the FPGA design group

Regards

Jose A.

Intel Customer Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think, my question is not for the FPGA design thou...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @ZShin:

Thank you for contacting Intel Embedded Community.

You need to verify that your design fulfills the requirements stated in section 14, on pages 675 to 720 of the Intel(R) Xeon(R) Processor D-2100 Product Family Platform Design Guide [PDG] document # 568130.This document can be found when you are logged into your Resource & Design Center (RDC) privileged account on the following website:

http://www.intel.com/cd/edesign/library/asmo-na/eng/568130.htm

The RDC Account Support form is the channel to process your account update request or any inconvenience related to the provided websites. It can be found at:

https://www.intel.com/content/www/us/en/forms/support/my-intel-sign-on-support.html

Best regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page