- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm a new Verilog programmer and still rely on examples to write code.

I didn't find any example of what I need.

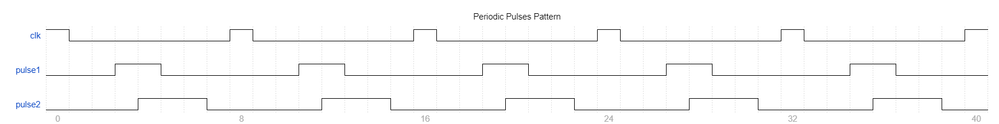

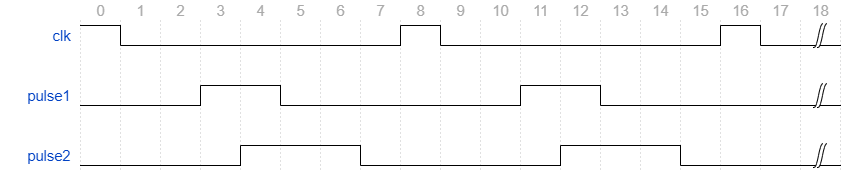

I need to generate two pulses periodicaly like this following schema:

clk is the base of the period (pulse every 8 ticks for example).

pulse1: rises 3 ticks after positive edge of clk and falls 2 ticks later.

pulse2: rises 4 ticks after positive edge of clk and falls 3 ticks later.

I'd like also generates the pulses for a limited number (N) of periods, 1 ≤ N < ∞.

I suppose I have to use temporisation conditions (#t) but didn't success to synchronize them to posedge of clk.

Thank for your help.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for using Intel Communities.

Please allow some time while I investigate.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Are you trying to do this for simulation only? Are you trying to have a testbench to show this behaviour?

Can you share what you currently have?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you to your answer,

Yes it is for a testbench only. I have no result because I didn't find how writing the code to obtain the desired result.

Best regards.

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Can you attach the code you have written so we can work from there?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

That doesn't look like a testbench. How are you simulating this? Are you using ModelSim/QuestaSim?

I tried using QuestaSim and managed to get the output you want.

First of all, a testbench shouldn't have any ports declaration -> module Pulses(clk, pulse1, pulse2);

It should be empty like so -> module Pulses ();

And I don't think you can use assign in testbench.

Please refer to the verilog files I'm attaching. periodic_pulses.v is the top verilog file in your Quartus project and periodic_pulses_tb.v is the testbench.

Follow the steps here to compile and run simulation, it should be the same for Quartus Lite:

QuestaSim: https://www.intel.com/content/www/us/en/docs/programmable/703090/21-1/simulation-quick-start.html

ModelSim: https://www.intel.com/content/www/us/en/docs/programmable/683248/18-0/simulation-quick-start.html

Regards,

Nurina

p/s: If any answer from the Intel Support is helpful, please feel free to provide rating with 4/5 survey on the support provided.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

apart from the point that outputs have no purpose in a testbench, the problem in your original code are of different kind.

Assignment must take place outside the initial statement.

`timescale 1us/1ns

module Pulses(clk, pulse1, pulse2);

output reg clk, pulse1, pulse2;

reg c, p1, p2;

initial

begin

c = 0;

p1 = 0;

p2 = 0;

repeat(1000) //1000 cycles repeated

begin

#0 c = 1;

#1 c = 0;

#2 p1 = 1;

#1 p2 = 1;

#1 p1 = 0;

#2 p2 = 0;

#1 ;

end

end

assign clk = c;

assign pulse1 = p1;

assign pulse2 = p2;

endmodule

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page