- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Inter Support and Expert,

I am reading JESD204B Intel® FPGA IP User Guide ( Quartus 21.3, IP 19.2.0)

in the document, there are a lot of registers, transmitter and receiver registers.

I didn't find any description in the document about how to operate these registers, for example read and write. I guess it will be through the dynamic reconfiguration. if I disable the dynamic reconfiguration features. does this mean that all the registers will be fixed value after the compile.

here is the example

4.7.2. Transmitter Registers

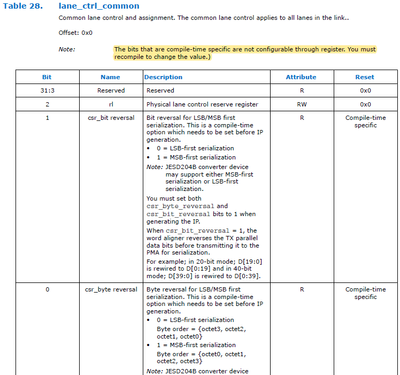

Table 28. lane_ctrl_common

Common lane control and assignment. The common lane control applies to all lanes in the link..

Offset: 0x0

is the reconfig_avmm_[interface] the way to access the registers? what would happen if I do not enable the Transceiver Dynamic reconfiguration?

Thank you ,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David'Enable Transceiver Dynamic Reconfiguration' option is to dynamically reconfigure the transceiver PHY CSR.

For register map of TX/RX CSR parameters, this option is not mandatory.

However, if you particularly want to dynamically reconfigure this lane_ctrl_common at offset 0x0,

Table 28 of this ug_jesd204b 683442-730782 mentioned that lane_ctrl_common is a compile-time option which needs to be set before IP generation. The bits that are compile-time specific are not configurable through register.

You can set it in JESD204B IP GUI.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David

Users can dynamically change the configuration of the JESD204B IP core base and PHY layers through TCL scripts (System Console control) or through embedded C programming (Nios subsystem control).

Kindly refer to 'JESD204B Intel® Arria® 10 FPGA IP Design Example User Guide"

HTML: https://cdrdv2.intel.com/v1/dl/getContent/683113

PDF: https://www.intel.com/content/www/us/en/docs/programmable/683113/

The structure of the design example varies depending on the values of these JESD204B IP core parameters:

• Data path:

Duplex: Both TX and RX data paths and CSR interfaces present

TX only: Only TX data path and CSR interface present

RX only: Only RX data path and CSR interface present

• Transceiver dynamic reconfiguration mode:

- When enabled, transceiver PHY reconfiguration interface is present in the design example and connected the JTAG to Avalon master bridge (System Console control) or Nios subsystem (Nios control) module.

- When disabled, transceiver PHY reconfiguration interface not present in design example.

The generated design example is a self-contained system with its own JESD204B IP

core instantiation that is separate from the IP core that is generated from the IP tab.

The JESD204B IP base core and PHY layer connect to System Console or Nios

subsystem through the Avalon memory-mapped interconnect. The JESD204B IP core

uses three separate Avalon memory-mapped ports:

• Base core TX data path— For dynamic reconfiguration of the TX CSR parameters

• Base core RX data path— For dynamic reconfiguration of the RX CSR parameters

• PHY layer— For dynamic reconfiguration of transceiver PHY CSR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Skbeh

I think I didn't ask my question clearly. on the block diagram, page 90 of ug_jesd204b 683442-730782, there are two Avalon MM interfaces.

one is reconfig_avmm* which is under the Tranceiver interface

one is Avalon-mm interface.

are Receiver Registers for example lane_ctrl_common at offset 0x0 accessible for both Avmm interfaces.

reconfig_avmm can alter some of the registers on the run. if not enable the dynamic reconfiguration parameter.

all the register can only be accessed during the configuration phase, not during the run time.

is my understanding correct?

Thank you very much,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David'Enable Transceiver Dynamic Reconfiguration' option is to dynamically reconfigure the transceiver PHY CSR.

For register map of TX/RX CSR parameters, this option is not mandatory.

However, if you particularly want to dynamically reconfigure this lane_ctrl_common at offset 0x0,

Table 28 of this ug_jesd204b 683442-730782 mentioned that lane_ctrl_common is a compile-time option which needs to be set before IP generation. The bits that are compile-time specific are not configurable through register.

You can set it in JESD204B IP GUI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page