- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

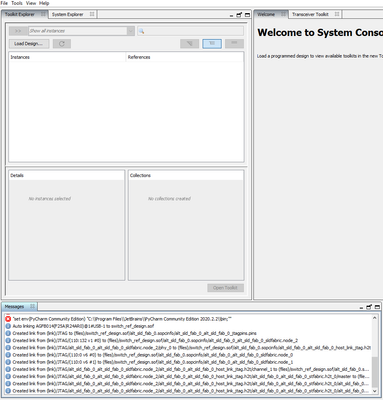

Issue Description: I enabled 'Debug Toolkit' feature of P-tile AVST PCIe Hard IP in Quartus and could see the PCIe endpoint in Linux, but No DUT listed in System Console after Load Design.

Tried Quartus Pro 20.1/20.2/21.1, same issue.

Hardware: AGF dev kit

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Do you see any other error message in debug toolkit ?

Also, have you done following as explained in P-tile user guide doc (page 164) ?

- When you run a dynamically-generated design example on the Intel Development Kit, make sure that clock and reset signals are connected to their respective sources and appropriate pin assignments are made. Here are some sample .qsf assignments for the Debug Toolkit:

- set_location_assignment PIN_A31 -to p0_hip_reconfig_clk_clk

- set_location_assignment PIN_C23 -to xcvr_reconfig_clk_clk

The reconfig_clk should be around 100MHz to 125MHz.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi dlim,

I do not see any errors in debug toolkit as blow:

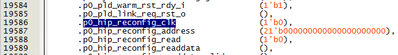

As for the assignment, I assign a 100M clk to xcvr_reconfig_clk_clk, but for p0_hip_reconfig_clk_clk, I quartus assign it to 0 after platform designer generation as below:

I check the toolkit clk and reset signals as below:

- Tags:

- dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Can you try pull "p0_hip_reconfig_clk_clk" to your top level project file and assign to input clock pin as suggested by the P-tile user guide doc ?

Also ensure your Agilex dev kit board is supplying correct clocking frequency to both the reconfig_clk pins.

The other thing that you can check is to verify reconfig_reset signal if available is not stuck in reset also.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Just to follow up is it working on your side now ?

Thanks

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

I do not receive any response from you to the previous question/reply/answer that I have provided in Feb.

This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel support agent.

Otherwise, the community users will continue to help you on this thread.

Thank you.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page