- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

wire [8:0] DL_0;

reg [8:0] R_0;

DelayLine #(1) DLIN_0 (enable, DL_0[0]);

genvar k_0;

generate

for (k_0=1; k_0<9; k_0=k_0+1) begin : generate_rdels_0

DelayLine #(1) DLK_0 (

.in(DL_0[k_0-1]),

.out(DL_0[k_0])

);

end

endgenerate

genvar j_0;

generate

for (j_0=0; j_0<9; j_0=j_0+1) begin : generate_regs_0

always @(negedge DL_0[j_0]) begin

R_0[j_0] <= node[0];

end

end

endgenerate

Can anyone help me with this? I've played around with the settings for the compiler and fitter to no avail (turned off register duplication, etc.)

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you provide the design.qar for investigation? What is the software version?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any updates?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi NChar7,

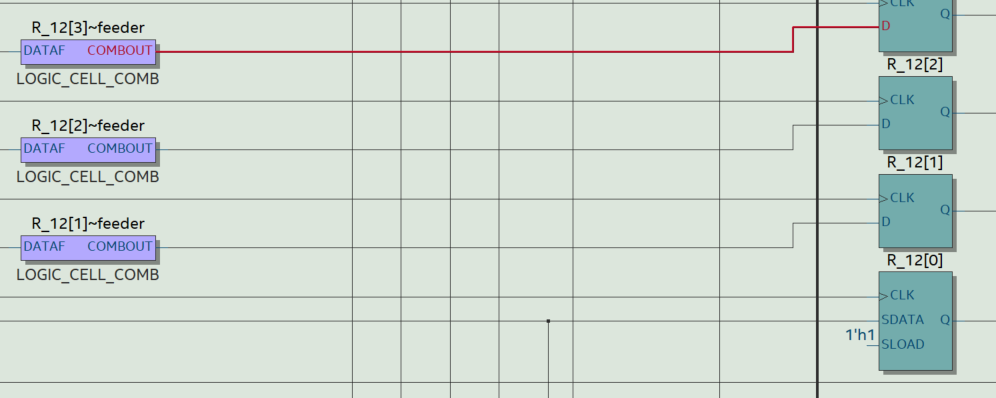

i am FPGA beginer, i also got this '~feeder', but i don't know what it stands for? I'm confused where this '~feeder' comes from and what does it mean?

Did you get any ideal about it?

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page