- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

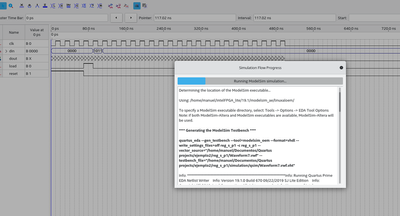

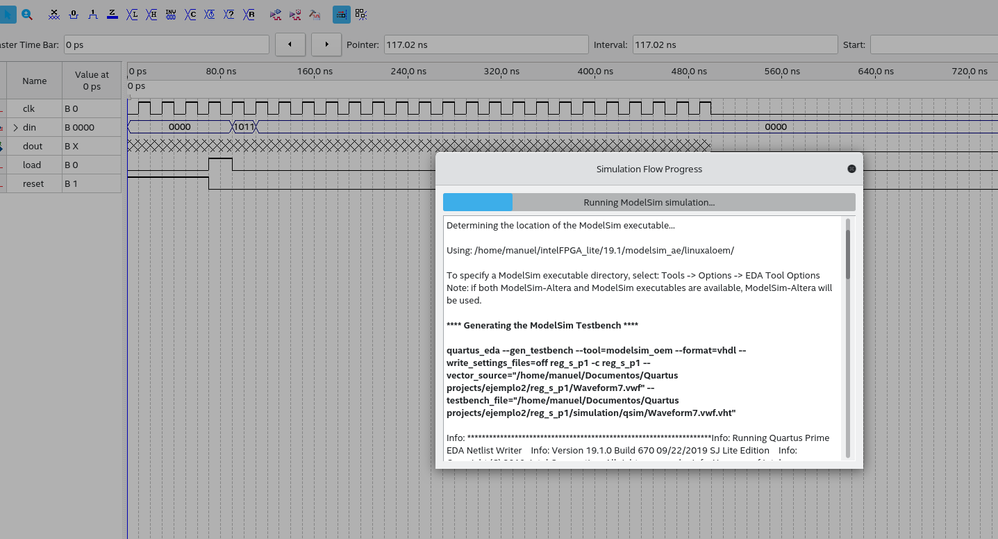

Hello everyone, I have installed Quartus in debian, and when I simulate in "University Program VWF" it gets stuck and does not finish the process. The truth is that I have no idea how to solve it, please I need help.

Determining the location of the ModelSim executable...

Using: /home/manuel/intelFPGA_lite/19.1/modelsim_ae/linuxaloem/

To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool Options

Note: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used.

**** Generating the ModelSim Testbench ****

quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p1 -c reg_s_p1 --vector_source="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/Waveform7.vwf" --testbench_file="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/Waveform7.vwf.vht"

Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: https://fpgasoftware.intel.com/eula. Info: Processing started: Mon Mar 18 01:01:27 2024Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p1 -c reg_s_p1 --vector_source="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/Waveform7.vwf" --testbench_file="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/Waveform7.vwf.vht"Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

Completed successfully.

**** Generating the functional simulation netlist ****

quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/" reg_s_p1 -c reg_s_p1

Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: https://fpgasoftware.intel.com/eula. Info: Processing started: Mon Mar 18 01:01:28 2024Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/" reg_s_p1 -c reg_s_p1Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.Info (204019): Generated file reg_s_p1.vho in folder "/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim//" for EDA simulation toolInfo: Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning Info: Peak virtual memory: 1101 megabytes Info: Processing ended: Mon Mar 18 01:01:28 2024 Info: Elapsed time: 00:00:00 Info: Total CPU time (on all processors): 00:00:00

Completed successfully.

**** Generating the ModelSim .do script ****

/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/reg_s_p1.do generated.

Completed successfully.

**** Running the ModelSim simulation ****

/home/manuel/intelFPGA_lite/19.1/modelsim_ae/linuxaloem//vsim -c -do reg_s_p1.do

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did you still stuck at this issue? Have you checked the spec machine requirement to run this? any background task running?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to https://supporttickets.intel.com/, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 5/5 survey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

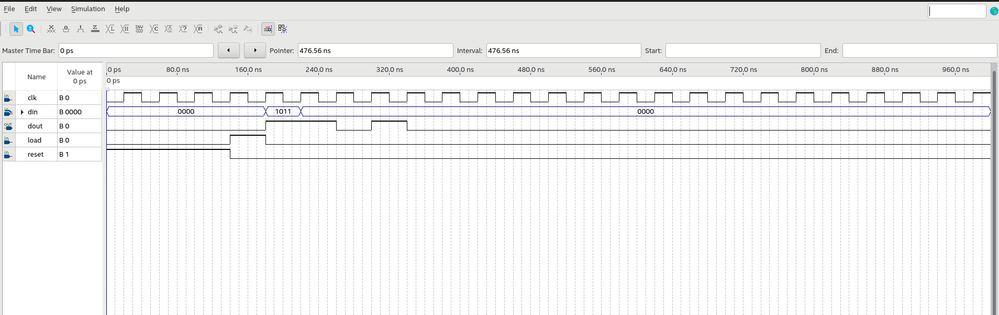

1. The first error I couldn't fix so I left it for a couple of days, then I restarted the machine and I had the debian operating system for updates, so I did it; after updating and opening quartus I got another error:

2.Now the problem was to add i386 architecture, also Install libX11.so.6, libxext6:i386, libxft2:i386 library; and the error is this:

Determining the location of the ModelSim executable... Using: /home/manuel/intelFPGA_lite/19.1/modelsim_ase/linuxaloem/ To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool Options Note: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used. **** Generating the ModelSim Testbench **** quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p21 -c reg_s_p21 --vector_source="/home/manuel/Documentos/reg_s_p21/Waveform5.vwf" --testbench_file="/home/manuel/Documentos/reg_s_p21/simulation/qsim/Waveform5.vwf.vht" Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: https://fpgasoftware.intel.com/eula. Info: Processing started: Tue Mar 26 16:55:11 2024Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p21 -c reg_s_p21 --vector_source=/home/manuel/Documentos/reg_s_p21/Waveform5.vwf --testbench_file=/home/manuel/Documentos/reg_s_p21/simulation/qsim/Waveform5.vwf.vhtWarning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance. Completed successfully. **** Generating the functional simulation netlist **** quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/reg_s_p21/simulation/qsim/" reg_s_p21 -c reg_s_p21 Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: https://fpgasoftware.intel.com/eula. Info: Processing started: Tue Mar 26 16:55:12 2024Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory=/home/manuel/Documentos/reg_s_p21/simulation/qsim/ reg_s_p21 -c reg_s_p21Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.Info (204019): Generated file reg_s_p21.vho in folder "/home/manuel/Documentos/reg_s_p21/simulation/qsim//" for EDA simulation toolInfo: Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning Info: Peak virtual memory: 1101 megabytes Info: Processing ended: Tue Mar 26 16:55:12 2024 Info: Elapsed time: 00:00:00 Info: Total CPU time (on all processors): 00:00:00 Completed successfully. **** Generating the ModelSim .do script **** /home/manuel/Documentos/reg_s_p21/simulation/qsim/reg_s_p21.do generated. Completed successfully. **** Running the ModelSim simulation **** /home/manuel/intelFPGA_lite/19.1/modelsim_ase/linuxaloem//vsim -c -do reg_s_p21.do /home/manuel/intelFPGA_lite/19.1/modelsim_ase/linuxaloem//vish: error while loading shared libraries: libX11.so.6: cannot open shared object file: No such file or directory Error.

su

dpkg -add-architecture i386

apt-get update

apt-get dist-upgrade

apt-get -f install

apt-get clean

and that's it, it seriously took me two weeks to fix this problem.

I don't understand much English, that message is translate.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you tried to install necessary package for Linux for Quartus?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Quartus Prime Lite 19.1 University VWF simulation error may occur due to various reasons, such as incorrect settings, compatibility issues, or errors in the design. To troubleshoot this error, ensure that the simulation settings are configured correctly, check for any compatibility issues with the software version, and review the design for any potential errors or inconsistencies. Additionally, referring to the Quartus Prime documentation or seeking assistance from the manufacturer's support team can help resolve the issue effectively.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to https://supporttickets.intel.com/, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 5/5 survey

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page