- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have the following code:

hls_always_run_component void Target00(ihc::mm_master<word4_t,ihc::aspace<7>, ihc::awidth<32>, ihc::dwidth<32>, ihc::latency<0>, ihc::waitrequest<true> >& device_5, ihc::stream_in<word4_t>& module8_read, ihc::stream_out<word4_t>& module8_write) {

static int kernel_size;

static int height;

static int width;

static int go;

static unsigned long lImageSrc_addr;

static unsigned long result_array_addr;

static bool is_initialized = false;

if (!is_initialized) {

module_init(kernel_size, height, width, go, lImageSrc_addr, result_array_addr);

is_initialized = true;

}

unsigned char lImageSrc[76800];

unsigned char result_array[76800];

module_read_routing_712(HOST0_ID, module8_read, reinterpret_cast<word4_t*>(&lImageSrc_addr), 1);

module_read_routing_771(HOST0_ID, module8_read, reinterpret_cast<word4_t*>(&result_array_addr), 1);

module_read_routing_833(HOST0_ID, module8_read, reinterpret_cast<word4_t*>(&kernel_size), 1);

module_read_routing_889(HOST0_ID, module8_read, reinterpret_cast<word4_t*>(&height), 1);

module_read_routing_940(HOST0_ID, module8_read, reinterpret_cast<word4_t*>(&width), 1);

device_read_routing_993(DEVICEMEMORY_ID, device_5, reinterpret_cast<word4_t*>((unsigned int*)lImageSrc), lImageSrc_addr, 16);

device_read_routing_1074(DEVICEMEMORY_ID, device_5, reinterpret_cast<word4_t*>((unsigned int*)result_array), result_array_addr, 16);

module_read_routing_1164(HOST0_ID, module8_read, reinterpret_cast<word4_t*>(&go), 1);

unsigned long loffset = 0;

int kernel_half = (kernel_size - 1) / 2;

unsigned int pixel;

int private_kernel[7][7] = { 1 };

for (int i = 0; i < height; i++) {

for (int j = 0; j < width; j++) {

unsigned int sum = 0, x = 0, y = 0;

for (int ky = 0; ky < kernel_size; ky++) {

for (int kx = 0; kx < kernel_size; kx++) {

if (j + kx - kernel_half < 0) {

x = 0;

} else if (j + kx - kernel_half > width - 1) {

x = width - 1;

} else {

x = j + kx - kernel_half;

}

if (i + ky - kernel_half < 0) {

y = 0;

} else if (i + ky - kernel_half > height - 1) {

y = height - 1;

} else {

y = i + ky - kernel_half;

}

pixel = lImageSrc[x + y * width];

sum += ((int)pixel) * private_kernel[ky][kx];

}

}

// Put the result in output memory using a buffer

result_array[j + (i * width)] = (sum / 49);

}

}

device_write_routing_2218(DEVICEMEMORY_ID, device_5, reinterpret_cast<word4_t*>((unsigned int*)lImageSrc), lImageSrc_addr, 16);

device_write_routing_2300(DEVICEMEMORY_ID, device_5, reinterpret_cast<word4_t*>((unsigned int*)result_array), result_array_addr, 16);

module_write_routing_2388(HOST0_ID, module8_write, reinterpret_cast<word4_t*>(&go), 1);

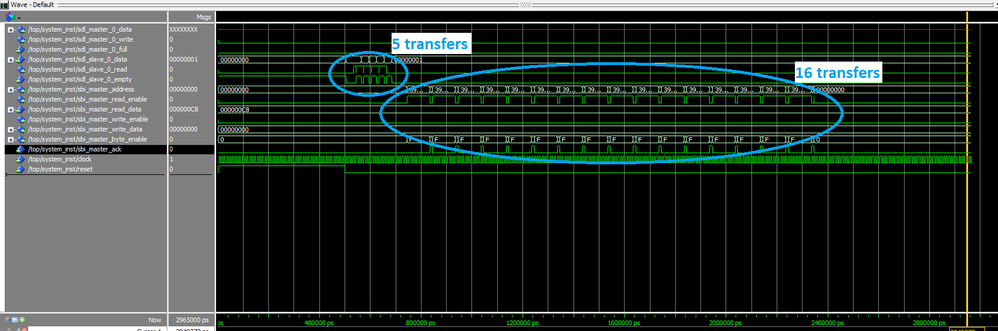

}The expected behavior is the following:

- Read 5 words from a streaming interface

- Read 16 words from a memory (memory map interface)

- Read 16 words from a memory (memory map interface)

- Read 1 word from a streaming interface

- Perform the algorithm (computation)

- Write 16 words to the memory (memory map interface)

- Write 16 words to the memory (memory map interface)

- Write 1 word to a streaming interface

In the generated component, the step 1 and 2 works! Steps 3, 4, 5, 6, 7 and 8 does not work. I even tried to comment out steps 3 and 4 to skip directly to the computation but I am not able to make the generated code performs steps 5, 6, 7 and 8.

At this point, I have no glue about what is going on. Can an Intel HLS engineer give me some input on this issue?

I have also attached the full cpp code + modelsim testbench.

Thanks,

Hubert

To give more context:

The step 1 is the group of function calls { module_read_routing_712, module_read_routing_771, module_read_routing_833, module_read_routing_889, module_read_routing_940 }

The step 2 is the call to device_read_routing_993.

The step 3 is the call to device_read_routing_1074.

The step 4 is the call to module_read_routing_1164.

The step 5 is the code between step 4 and 6.

The step 6 is the call to device_write_routing_2218.

The step 7 is the call to device_write_routing_2300.

The step 8 is the call to module_write_routing_2388.

- Tags:

- Hls

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The problem was with the avalon_mm_adapter. @HGuer2 will confirm that the message I sent him fixes the issue.

Sincerely

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The problem was with the avalon_mm_adapter. @HGuer2 will confirm that the message I sent him fixes the issue.

Sincerely

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »