- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have created a trivial design and confirmed that the ports with following type are completely ignored by Qsys in my custom component:

- signed

- unsigned

- integer

and

- record

Qsys (now platform designer) has been around for so many years. Why then is it that it cannot support these? I have found that Qsys completely ignores them as if they did not exist at all.

Why is even record type containing std_logic or std_logic_vectors ignored also? I just wanted to put all my conduit signals into a record so it is easier to connect them once exported, and Qsys does not permit record types as well! This is very strange.

The strangest thing is that, Qsys ignores them and generates no error message or warning!!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Why do you mention that it is being ignored? Can you attached your .v or .vhd files for me to verified?

You mention that qsys ignores them, do you mean it don't generate those port out for you to make connection if you use record?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

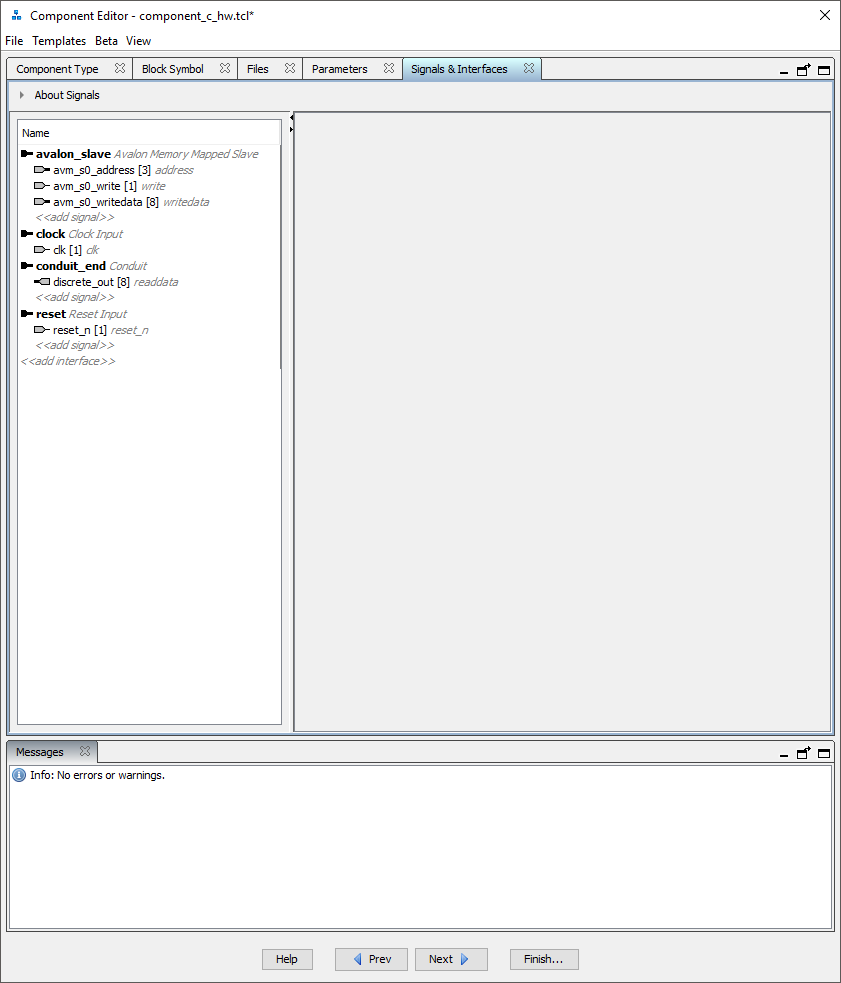

During the custom component generation, Qsys does not show them in the list of signals. This means that as far as Qsys is concerned, they do not exist. Therefore, they cannot be expected to appear on a custom component when we instantiate it in Qsys.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Got it, which means currently qsys had yet to support record type in the top level. which version of Quartus that you were using? Std or pro?

Can you give me the design? I will file enhancement on this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I replied with this attachment in the "under support request". However, it seems that my reply there did not show up here in forum post. I was wondering why I did not get a response to this attachment.

In the attached archive, please use the following files:

component_c.vhd

p_component_c.vhd

component_c_hw.tcl

The first two are the source files for this trivial component, the third is the _hw.tcl for use with qsys. You will notice that when you open the custom component editor, any port on the component that is not std_logic_vector is not shown, therefore you cannot add it into a conduit. Also, when you instantiate this component in Qsys, these ports will not appear. Qsys does not generate an error related to this, or warning. If it does not like any port other than std_logic and std_logic_vector then it must reject the component. However, why would Qsys be so restrictive in the first place, especially for signals that I just want to export into conduit anyway?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

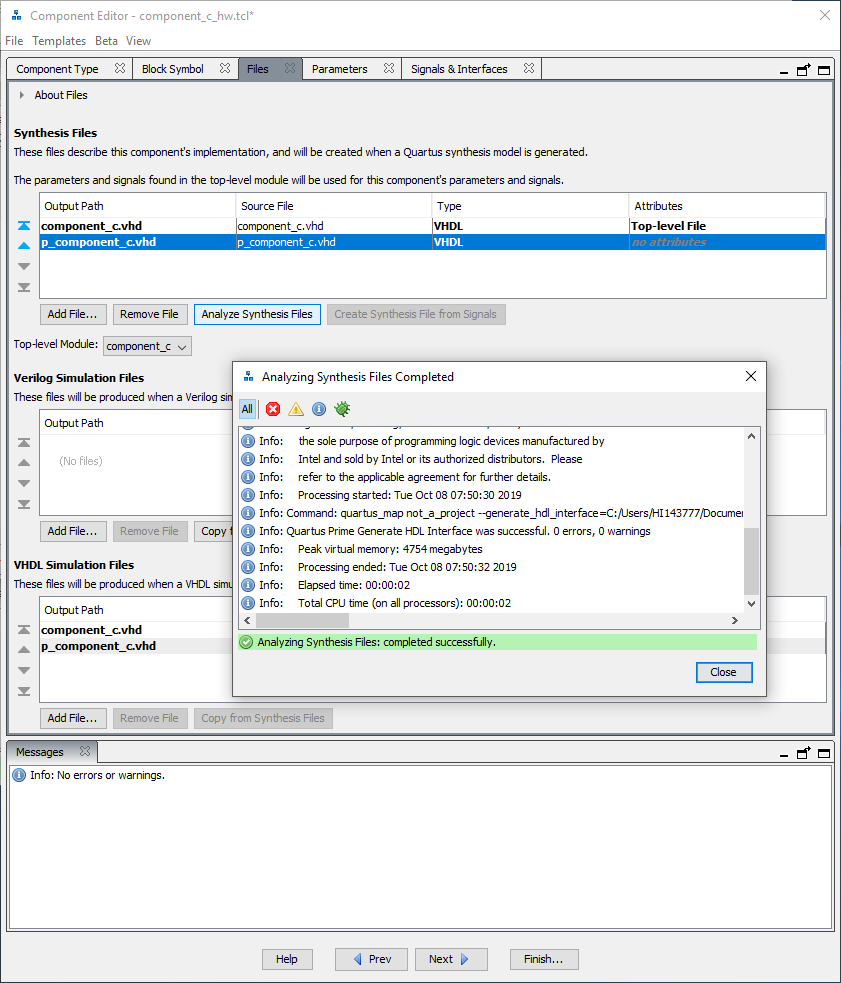

usually, the error was shown if you press on the analyze HDL files in the component editor:

Error: VHDL error at p_component_c.vhd(1): synthesis directive "vhdl_input_version" is not supported File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/p_component_c.vhd Line: 1

Error: Ignored construct p_component_c at p_component_c.vhd(16) due to previous errors File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/p_component_c.vhd Line: 16

Error: VHDL error at component_c.vhd(1): synthesis directive "vhdl_input_version" is not supported File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/component_c.vhd Line: 1

Error: VHDL Use Clause error at component_c.vhd(8): design library "altera_work" does not contain primary unit "p_component_c" File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/component_c.vhd Line: 8

Error: VHDL error at component_c.vhd(19): object "discrete_array_t" is used but not declared File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/component_c.vhd Line: 19

Error: VHDL error at component_c.vhd(23): object "record_out_t" is used but not declared File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/component_c.vhd Line: 23

Error: Ignored construct component_c at component_c.vhd(24) due to previous errors File: /data/ts_farm/kentan/2019/October/Forum_qsys_top_level_pro/component_c.vhd Line: 24

Error: Flow failed:

Warning: Quartus Prime Synthesis was unsuccessful. 8 errors, 0 warnings

Error: Peak virtual memory: 1231 megabytes

Error: Processing ended: Tue Oct 8 10:58:44 2019

Error: Elapsed time: 00:00:04

Error: System process ID: 46096

I will file an enhancement to our engineering on this. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

KTan_Intel, I am surprised you got so many errors. When I analyse these files in Qsys custom component editor, I do not get these.

I have attached an image as proof of this.

I have attached another image which shows that the Qsys custom component editor ignores any port that is not std_logic_vector. Please have a look.

If you are getting errors but I am not, then something really weird is going on here

I have deleted my first answer. If this forum is functioning correctly, you should not see 2 almost identical answers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which version of Quartus that you were using?

I try on Quartus prime std 19.1 and Quartus prime pro 19.3. Both have the same error.

Also, I am using linux version. Are you using windows version?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If that is the case, Q19.1 had been enhance to show error. I will just file enhancement to support this instead provide error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, some times. It would take times for our developer to look into it. Hope you can understand.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page