- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The following C++ code executes 4x more slowly in standard configuration (hello_world) compared to small configuration (hello_world_small).

I'm using a DE2-115 @ 50 MHz with 128 MB SDRAM @ 50 MHz.

What is the reason for this speed difference?

const short WIDTH = 320; // Pixels.

const short HEIGHT = 240; // Pixels.

const short FRAMES = 366; // Number of video frames.

short video [FRAMES][HEIGHT][WIDTH];

for (short f = 0; f < FRAMES; f++)

{

for (short y = 0; y < HEIGHT; y++)

{

for (short x = 0; x < WIDTH; x++)

{

video[f][y][x] = 0;

}

}

}Thanks,

Tim.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tim,

- When the "Reduced device drivers" option is checked, the compiler will include the reduced version of device drivers for all devices that provide small drivers. This reduces memory footprint at the expense of functionality. For example, the UART and JTAG UARTs use a polling method instead of an interrupt driven method.

- When the "Small C library" option is checked, the system library uses a reduced implementation of the C standard library. The reduced library is optimized for smaller memory footprint.

Based on above points it may be how design are implemented by compiler, Also

Duration of Avalon-MM transfer is variable,

Avalon-MM transfers transmit up to 1024 bits at a time, and take one or more clock cycles to complete(The shortest duration of an Avalon-MM transfer is one cycle).

One instruction per 6 clock cycles, so 6 cycle is the max.

However try optimizing the design that may help to reduce the timing.

Let me know if you need any further assistance.

Refer below two links

http://www-ug.eecg.toronto.edu/msl/manuals/n2cpu_nii5v1.pdf

https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/solutions/rd03102006_962.html

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anand,

Thanks for the info.

I'm using the NIOS 2/f in both configurations. Actually, it's exactly the same .qsys and .sopcinfo in both configurations because I have two software projects in the Eclipse software sub folder.

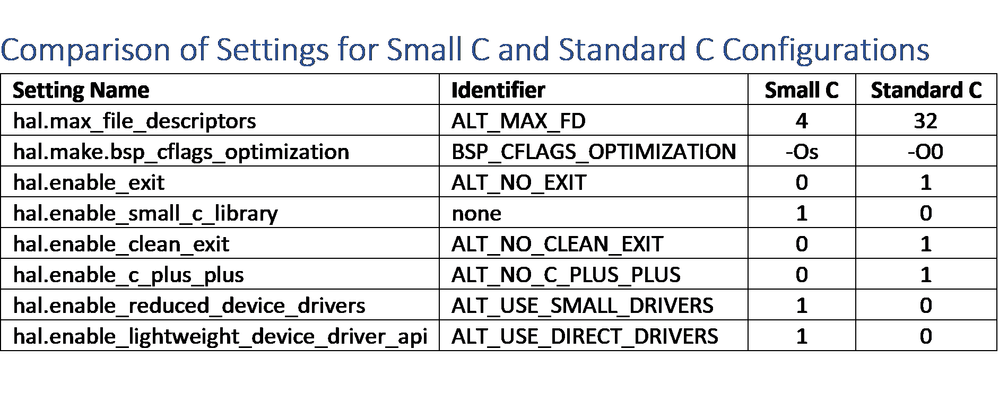

I used WinMerge to compare the two settings.bsp XML files. Here's what I found:

For the last column, I modified the standard BSP setttings to make them the same as the small BSP settings as a control test. Considering that there is a 5x speed difference, more is going on than I am aware of.

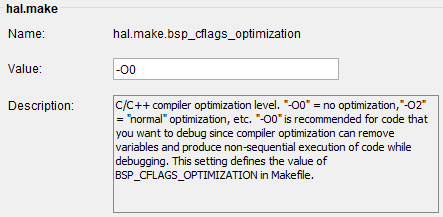

The description in the BSP Editor doesn't fully describe what the options mean, e.g. no mention of -Os.

I tried searching the PDF you linked to for the above settings and identifiers, e.g. BSP_CFLAGS_OPTIMIZATION and -O2 but nothing pertinent showed up.

Do you know where I can find detailed descriptions of the above parameters?

I found some info here: https://gcc.gnu.org/onlinedocs/gcc/Optimize-Options.html#Optimize-Options

And sorry to bother you about such basic stuff, but I'm struggling to find the info.

Thanks,

Tim.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tim,

-Os: This is the most important compiler switch when optimizing for space. This instructs compiler to optimize for space rather than speed

Please refer below link

https://www.intel.com/content/www/us/en/programmable/documentation/lro1419794938488.html

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page