- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have recently downloaded this tool and am attempting to utilize it on a custom Bay Trail design where I already customized the BIOS. We would like to use this tool to customize future BIOS images instead of changing the code. Our design utilizes memory down with no SPD device. I have embedded the SPD data into the BIOS. I would like to change the values in the Memory Initialization module but they are all grayed out and cannot be edited. How can I change these values? How can I integrate the SPD data into the BIOS?

- Tags:

- Firmware

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

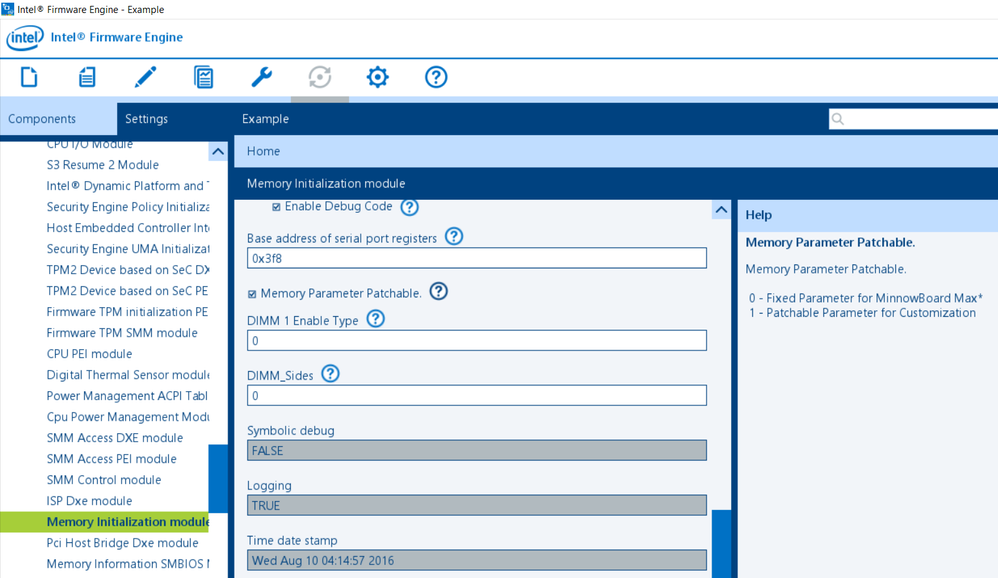

The MinnowBoard Max has a good example of memory-down configuration. You need to verify two settings in the 'Memory Initialization module' component before customizing the memory parameters.

Enable Memory Down = 1 (at the top of the list).

Memory Parameter Patchable = 1 (further down the list, below the debug settings).

Once you enable Memory 'Parameter Patchable' and hit 'Save' the grayed-out options will be available to edit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was able to change the parameters. Thanks!

What about the SPD data. In my current BIOS I have to provide the following parameter array.

typedef struct {

CONST UINT8 SpdPresent;

CONST UINT8 MemType;

CONST UINT8 MemModuleType;

CONST UINT8 SdramDensityBanks;

CONST UINT8 SdramAddressing;

CONST UINT8 NomVoltage;

CONST UINT8 ModOrganization;

CONST UINT8 ModMemBusWidth;

CONST UINT8 FineTimebaseDividend;

CONST UINT8 MedTimebaseDividend;

CONST UINT8 MedTimebaseDivisor;

CONST UINT8 MinCycleTime;

CONST UINT8 Rsrvd1;

CONST UINT8 CASLatenciesLsb;

CONST UINT8 CASLatenciesMsb;

CONST UINT8 MinCASLatencyTime;

CONST UINT8 MinWriteRecoveryTime;

CONST UINT8 MinRASToCASDelayTime;

CONST UINT8 MinRowActiveDelayTime;

CONST UINT8 MinRowPrechargeDelayTime;

CONST UINT8 UpperNibblesForRASAndRC;

CONST UINT8 MinActiveToPrechargeDelayTime;

CONST UINT8 MinActiveToRefreshDelayTime;

CONST UINT8 MinRefreshRecoveryDelayTimeLsb;

CONST UINT8 MinRefreshRecoveryDelayTimeMsb;

CONST UINT8 MinWriteToReadCommandDelay;

CONST UINT8 MinReadToPrechargeCommandDelay;

CONST UINT8 UpperNibbleTfaw;

CONST UINT8 MinFourActivateWindowDelay;

CONST UINT8 OptionalFeatures;

CONST UINT8 ThermalAndRefreshOptions;

CONST UINT8 ModThermalSensor;

CONST UINT8 DeviceType;

CONST UINT8 rsrvd2[26];

CONST UINT8 ModTypeSpecificSection[57];

CONST UINT8 ModJedecIdCode[2];

CONST UINT8 ModManufacturingLocation;

CONST UINT8 ModManufacturingDate[2];

CONST UINT8 ModSerialNumber[4];

CONST UINT8 CRC[2];

} OEM_MRC_DIMM_MATRIX;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you're hard-coding parameters in Intel Firmware Engine, then you don't need to provide full SPD data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I added the custom memory parameters we require, and the board will boot up to Port 80 code 0x2F which is at the end of the memory initialization sequence (function SetInitDone I believe). Any idea why I could be freezing at this point?

Another question: Is dual-core the only version of Bay Trail supported?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Using an emulator, I was able to determine that the memory initialization was using the Fast Boot Path (FBPath). I built the BIOS with Fast Boot disabled, and it now took the S5 Path (S5Path) for memory initialization. It still stops booting at code 012Fh. Since this is the last step of the memory init sequence, I don't know if I have completed the init and locked up at the next BIOS step. What BIOS function is immediately after the memory init?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

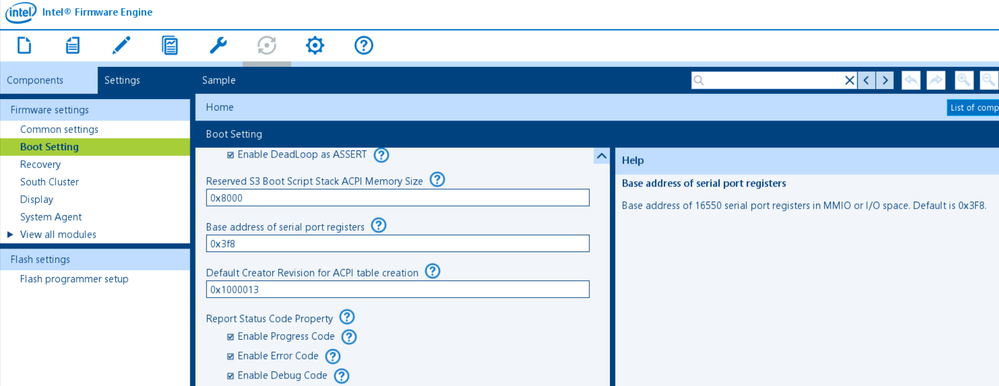

It looks like I am stuck in a loop where the BIOS is trying to communicate with a serial port at address 3F8h. Am I required to have a serial port at this address? How can I disable this feature?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

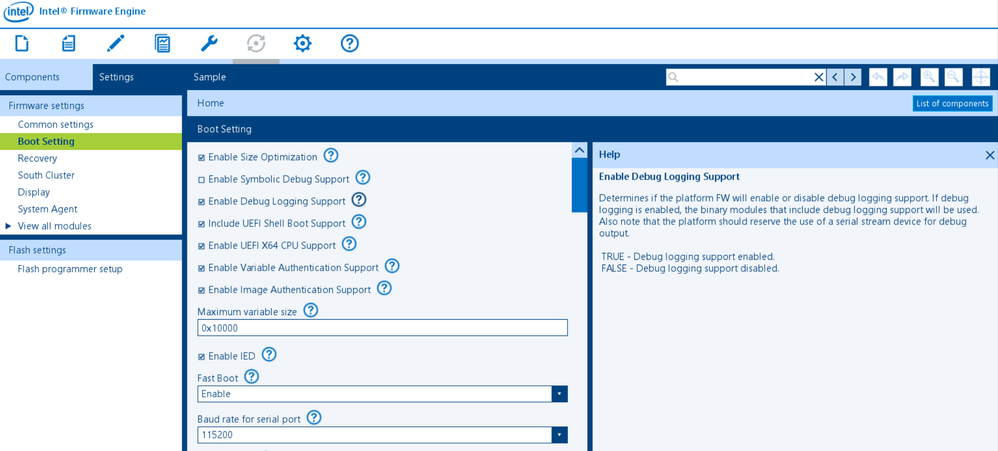

The default implementation uses a serial port as an error console. This is based on the MinnowBoard Max/Turbot design. There are several items you can modify.

Enable/disable debug mode & debug console output:

Default is to enable debug logging on the serial port. You can disable this option to optimize the build for release, and disable debug strings being sent via the serial port.

Note: if you have a serial port, the debug output would be useful in solving your memory timing issue.

Change Serial Port Address/Parameters:

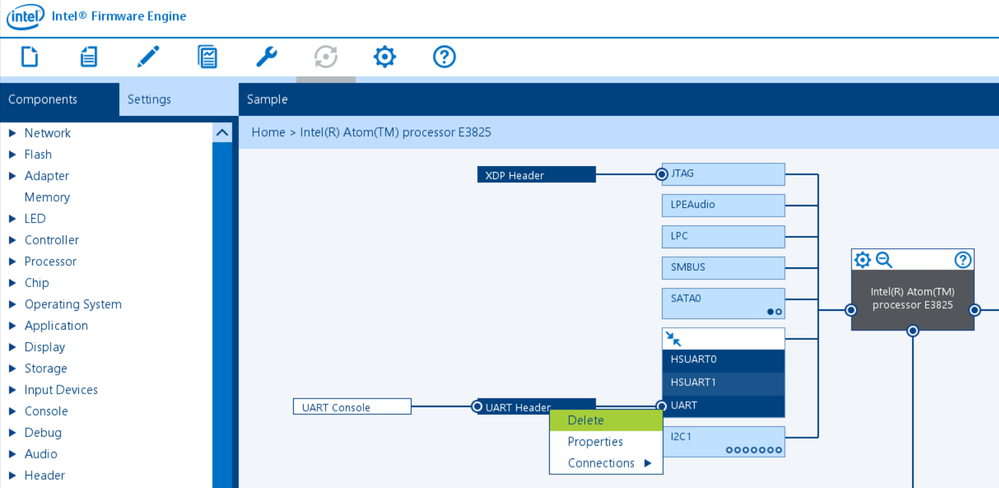

Remove serial port from design:

Expand the Intel processor component to see the full system map. Delete the header form the Serial UART.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I deleted the UART with no luck. Still stops at 012Fh.

Unfortunately our UART ports go through a Lattice FPGA which defaults to disabled. I can generate a custom programming file that enables one of the ports at 3F8h. Is there any sort of USB debug port provided?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which parameters did you change? What exact values they are? I will try to duplicate in my side.

Evan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a custom SBC based on the Bay Trail processor that uses an in-house BIOS based on the Phoneix Secure-Core Technology version 3.1. The memory settings I am using are from that BIOS. Here are the settings I am using in the Firmware Engine:

// hardcode values for C407 DDR3L memdown

Input_Struct.Rank_En[0][0] = 1; /**< [Channel][Rank] Ranks Present with MAX_RANKS defined in Imemory.h */

Input_Struct.Rank_En[0][1] = 0; /**< [Channel][Rank] Ranks Present with MAX_RANKS defined in Imemory.h */

Input_Struct.Rank_En[1][0] = 0; /**< [Channel][Rank] Ranks Present with MAX_RANKS defined in Imemory.h */

Input_Struct.Rank_En[1][1] = 0; /**< [Channel][Rank] Ranks Present with MAX_RANKS defined in Imemory.h */

Input_Struct.DIMM_DWidth[0][0] = 0x1; /**< [Channel][Slot] DIMM0 DRAM device data width 00:x8, 01:x16, 02:x32*/

Input_Struct.DIMM_Density[0][0] = 0x2; /**< [Channel][Slot] DIMM0 DRAM device data density 00:1Gbit, 01:2Gbit,02:4Gbit,03:8Gbit*/

Input_Struct.DRAM_Speed = 0x1; /**< 00:800, 01:1066, 02:1333, 03:1600 */

Input_Struct.DRAM_Type = 0x1; /**< 00:DDR3, 01:DDR3L, 02:DDR3U, 04:LPDDR2, 05:LPDDR3, 06:DDR4 */

Input_Struct.DIMM_MemDown = 0x1; /**< 0:DIMM, 1:Memory Down */

Input_Struct.DIMM_BusWidth[0][0] = 3; /**< [Channel][Slot] 000:8 bits; 01:16bits, 02:32bits, 03:64bits */

Input_Struct.DIMM_Sides[0][0] = 0; /**< [Channel][Slot] ranks per dimm 00:1rank, 01:2ranks, 02:3ranks, 03:4ranks */

Input_Struct.tCL = 7; /**< actual CL */

Input_Struct.tRP_tRCD = 7; /**< TRP and tRCD in dram clk - 5:12.5ns, 6:15ns, 7:*/

Input_Struct.tWR = 8; /**< in dram clk */

Input_Struct.tWTR = 4; /**< in dram clk */

Input_Struct.tRRD = 4; /**< in dram clk */

Input_Struct.tRTP = 4; /**< in dram clk */

Input_Struct.tFAW = 20;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you tried the latest Intel firmware Engine?

Port 80 0x12F is the last check point we have in bios code, so it doesn't mean there are something wrong with MRC init.

BTW, I ever tried your parameters on our board, it can boot to shell.

As I mentioned in the beginning, nobody will access port 80 anymore after MRC init. Maybe bios code has run far away from MRC. We can not make sure where it is now without debug log.

Can you help to enable "Enable Symbolic Debug Support" option, see what will happen?

You can find this option from "Settings --> Boot setting " as the second pic Brain attached above.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the assistance. I disabled all of the debug options since I never get any data on my console.

I agree that I am getting past the memory initialization code. Using the emulator, I can confirm that plenty of code is being executed after the memory init and that no further port 80 writes occur.

So why is my boot still freezing? I eventually stop at a halt instruction. I never get any video output on a VGA or Display Port monitor. I have added both monitor types to the component diagram. Why do they attach to the HDMI box?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1

Your board still hang without video output even "Enable Symbolic Debug Support" is enabled, right ?

If yes, let us continue to narrow down the issue together.

MinnowBoard Max open source image can be found in

(https://firmware.intel.com/projects/minnowboard-max ) , you can download debug version and check if your board can boot to shell. That can help us make sure whether there is a hardware issue with your board or not.

2.

In the other hand, please help to list details hardware component information of your design board, such as CPU type, Flash vendor .......

We use different SPI flash in MinnowBoard Max and MinnowBoard Turbot,which might be one of root cause the board can't boot. So make sure which kind of boards do you have in hand?

3. There is a very detailed introduction about MinnowMax board, http://wiki.minnowboard.org/MinnowBoard_MAX

In MinnowBoard MAX Board Layout section, help us check if you can find "FTDI serial" in the board, do you have a cable with 6 pin to connect it?

Once you update debug version image to your board, you can get log info from FTDI serial port.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After comparing schematics for the two boards, we are using different UART ports so I do not believe this will ever work. Our UART1 at 3F8h is on a programmable device connected to the LPC bus. I do not see any way I can add the console to the LPC block.

If I disable the console and debugging, the BIOS does not lock up in a UART loop but still does not boot. It runs until it executes a halt instruction.

Our board uses a E3825 processor and a Numonyx N25Q064A11 flash device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can anyone of following Opensource images boot to shell in your board?

https://firmware.intel.com/projects/minnowboard-max

MinnowBoard MAX 0.93 64-Bit: Debug -- Release

MinnowBoard MAX 0.93 32-Bit Debug -- Release

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page