- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to write to and read from on-chip FIFOs from a C program running on a PC connected to an FPGA(Stratix V). I have been reading non-stop on the internet for the past week and I've come across a lot of different key concepts but can't get a big picture together that would allow me to have the understanding to implement the data transfer on my own.

I did however find an example program on the user-guide disk that inplemented the PCIE interface as well as writing to on-chip memory and DDR3 memory, and included a C library that I could use on the PC side that contained

PCIE_Read32(), PCIE_DmaRead() and their write counterparts.

Since I still don't fully understand how the whole PCIE/DMA/AVALON system works, I would really appreciate input on how to connect a FIFO to this system on the Platform designer.

I tried connecting the read master of the PCIE to the out of the fifo, and the write master of the PCIE(v-series mm dma for pci express) to the in of the fifo but I got the following errors:

"Error:[...] pcie_256_dma.dma_wr_master is read-only while pcie_256_dma.dma_wr_master is write-only. "

(which makes absolutely no sense)

and

"Error: [...]: fifo_0.out is read-only while pcie_256_dma.dma_rd_master is write-only."

Connecting them the other way around was accepted(I left the

in_csr and in_irq pins dangling because I don'know what to do with them) but that didn't work.

I will be adding a screenshot of the platform designer as soon as I can .

Here is the syntax I tried to used to access the FIFO from the PC:

#include "stdafx.h"

#include <stdio.h>

#include <stdlib.h>

#include <memory.h>

#include "PCIE.h"

#define DEMO_PCIE_USER_BAR PCIE_BAR4

#define FIFO_WRITE_MEM_ADDR 0x80020

#define FIFO_READ_MEM_ADDR 0x80024

...

BOOL bPass;

int* push;

bPass = PCIE_Read32(hPCIe, DEMO_PCIE_USER_BAR, FIFO_READ_MEM_ADDR,(DWORD)push);

and same for write.

what happens is that the "FIFO" behaves like a 32 bit register. I can only read the last value that I wrote, so if I write three times and then read, I will read the last write. If I keep reading I keep getting that last write, until I write again.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

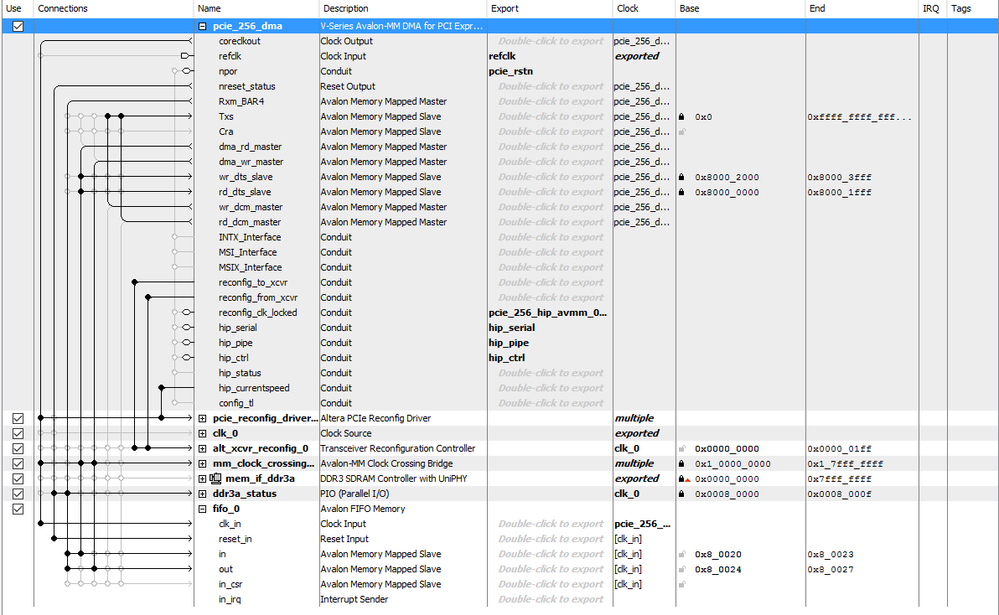

This is not relevant to my question. This is using the stratix hard ip for pci express. The reference design my question is about uses the v-series mm dma for pci express and therefore has completely different connections. I already have a PCIE system, I just want to connect a FIFO to it, not start over with another reference design that also has no explicit mention of FIFOs. Here is the screenshot of my system:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have managed to communicate with the fifo using PCIE_Write32/Read32() and was experimenting with Dma_Write(), which worked, and Dma_Read(), which didn't work.

I don't need further assistance with connecting the FIFO in the platform designer. It seems the configuration I posted in the screenshot does work. I will be posting an answer to my own question soon for others who might face the same confusions as I did.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page