- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

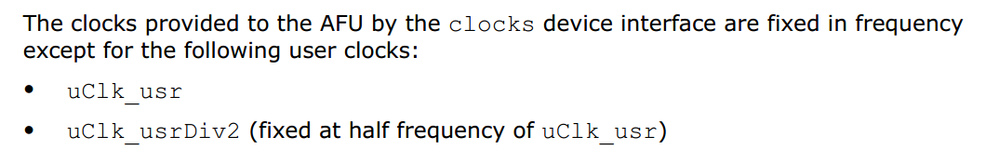

Please read the 5.3.2.1.7. Specify AFU User Clock Timing

Section in our Accelerator Functional Unit Developer’s Guide for Intel FPGA Programmable Acceleration Card:

https://www.intel.com/content/www/us/en/programmable/documentation/bfr1522087299048.html

Let me know if there is further questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

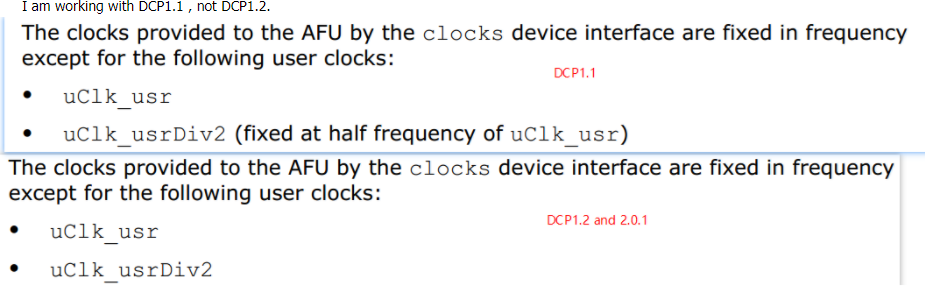

I am working with DCP 1.1, not 1.2 or 2.0.1

So this guide is not suitable for me.

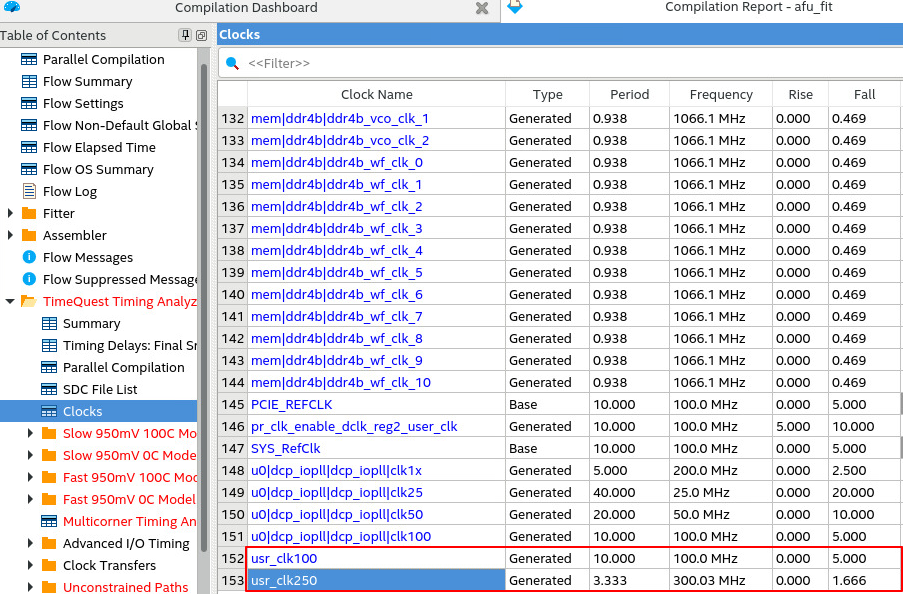

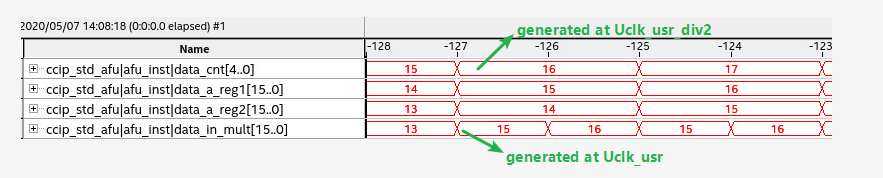

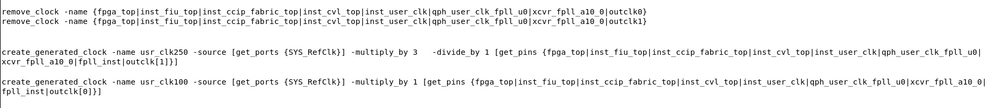

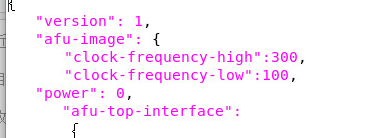

Please read the pictures in my attachment.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page