- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

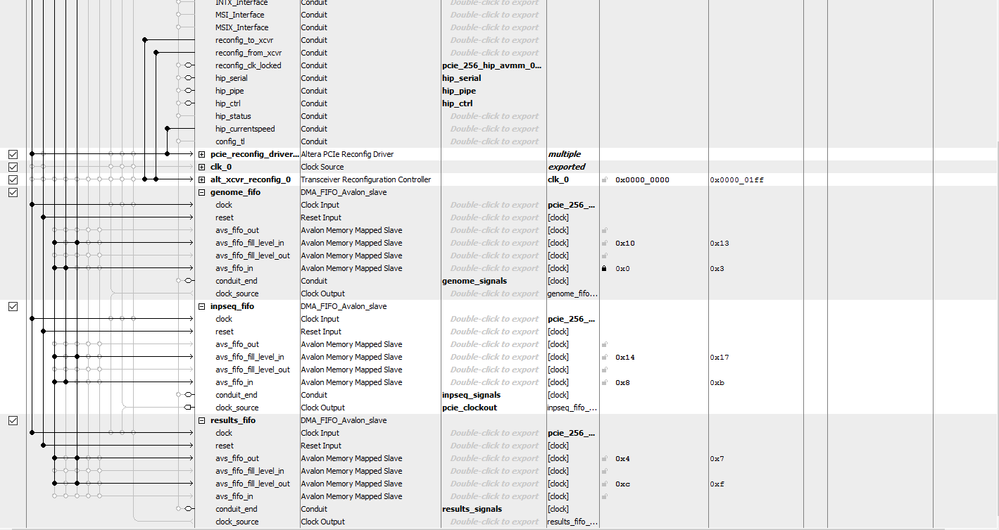

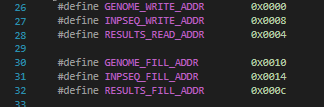

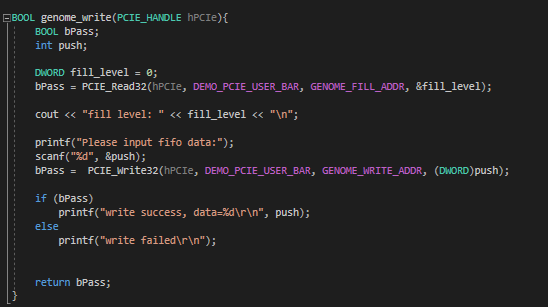

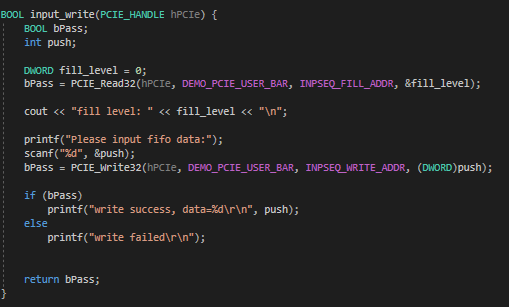

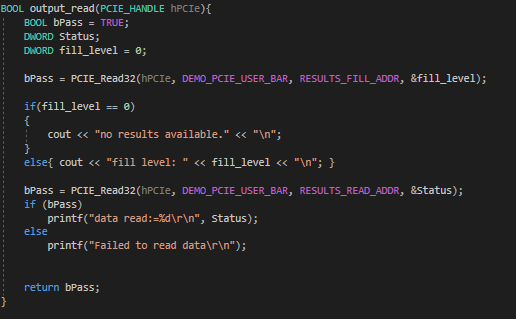

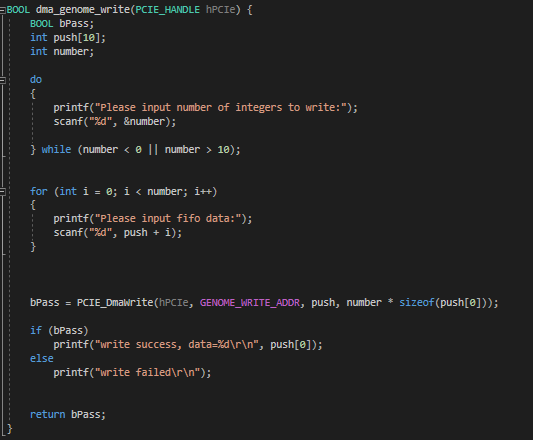

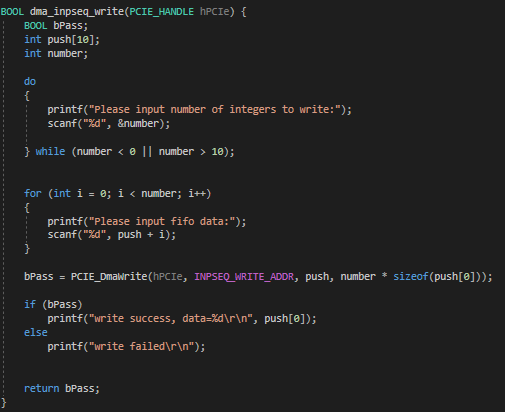

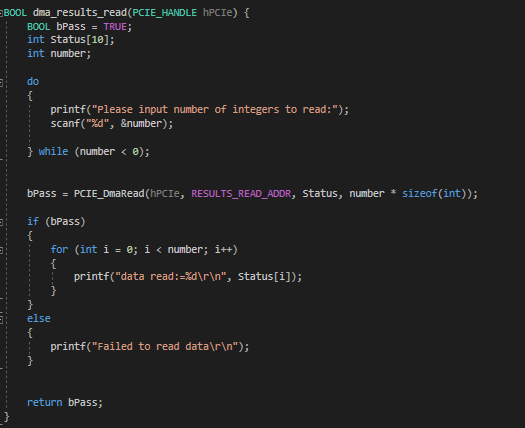

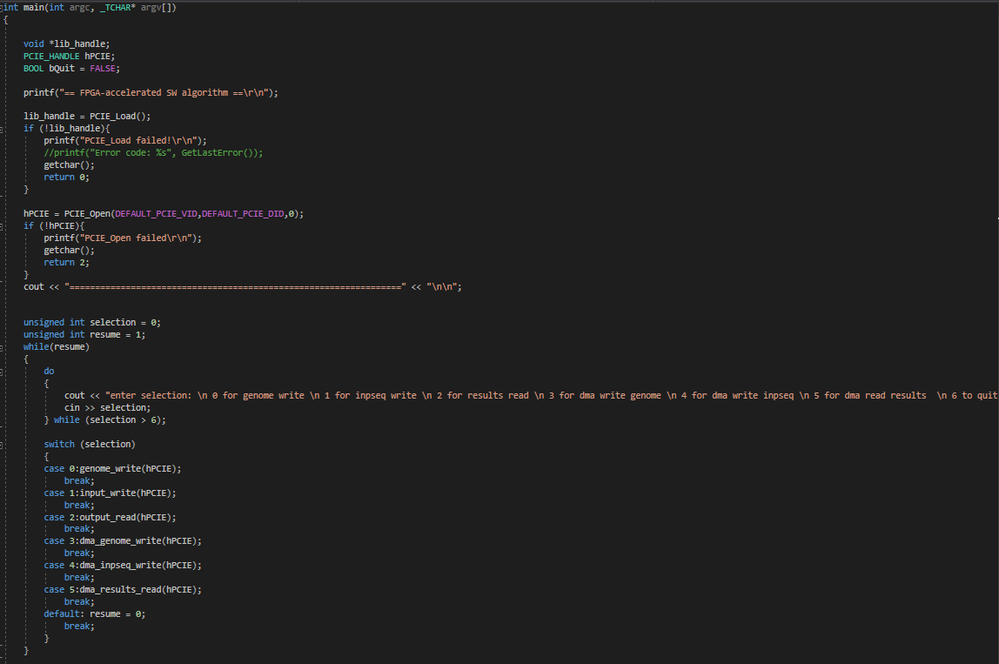

I am trying to transfer data between FIFOs on an FPGA and a C++ program running on a PC. I am using the PCIE example design from the DE5-net CD demos as a basis for my own. I have two FIFOs I am writing to and one I am reading from. I created an Avalon salve interface for communication with the FIFOs. On the PC side I am using the 4 functions PCIE_Read/Write32() and PCIE_DmaRead/Write() from the demo.

The read/write 32 functions are extremely slow and can only keep up with the FPGA if it's running at 2 MHz(I need to go to about 300). I am trying to use the DMA functions in the hopes that it will improve the speed of the data transfers. I am trying to send under 100 Mbytes per second, which should be a joke to PCIE, so there should definetly be a way to get it done.

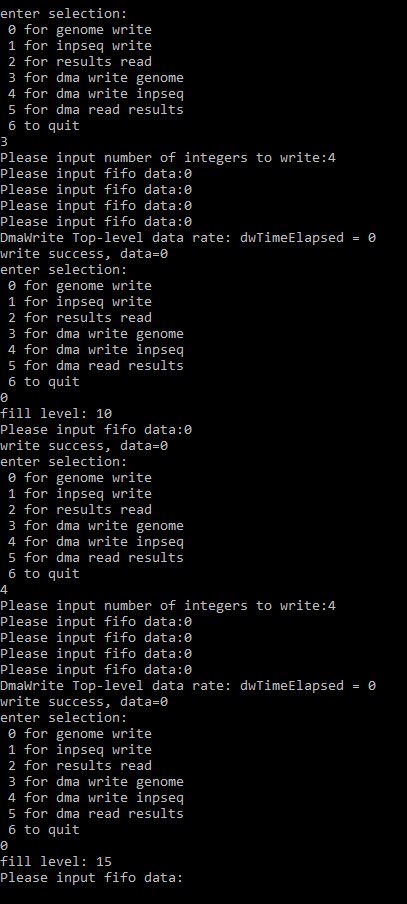

When i use the DMA functions to write to the two FIFOs, The write operation works, but it always writes to the same FIFO and not the other, regardless of which address I use in the argument of PCIE_DmaWrite(). It seems to always be writing to the FIFO with input adress 0x0. The dma read operation works without problems, though I only have one read-FIFO anyway. When I tried manually setting the base adresses so that neither of the write-FIFOS had base address 0x0, the C program crashes shortly after producing some false results, and then the PCIE_Open() will alwys return false.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

We can help you on how to debug the IP. but we can't give you support on the c-programming debug. can you help to use signaltap tools to capture the specific signal and determine how it fail to work?

Thanks!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page