The Intel® oneAPI Base Toolkit is a game-changer for enhancing productivity in the hardware development world. It enables software kernels written in SYCL* (C++) to be implemented quickly in FPGA hardware, revolutionizing how we develop IP blocks for Intel FPGAs.

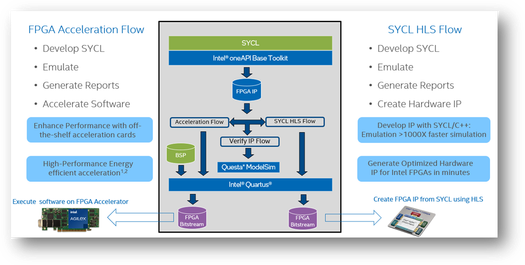

The Intel implementation of the oneAPI standard enables multiple development flows, providing two distinct development flows for FPGAs.

- In the FPGA Acceleration flow, oneAPI provides runtime acceleration of software algorithms, and the target is an Intel FPGA Acceleration platform.

- In the SYCL HLS flow, the target is an FPGA device, allowing optimized RTL IP blocks to be generated and imported directly into the Quartus hardware development environment.

This blog post focuses on using the SYCL HLS flow for Quartus RTL IP development. Existing Quartus users are only required to install the Intel oneAPI Base Toolkit.

Unleashing the Power of High-Level Synthesis for IP Development

In our fast-paced world, developing Intellectual Property (IP) for Intel Quartus using oneAPI and High-Level Synthesis (HLS) has become an essential strategy.

HLS is a process that translates high-level programming languages (C, C++, SYCL, etc.) into a hardware description language. We can reap numerous productivity benefits using HLS for IP development in Quartus. These benefits range from fast time-to-market to a more streamlined development process, which can significantly impact the bottom line of any tech-focused business.

- Increased Productivity: HLS allows designers to describe hardware behavior at a higher abstraction level, leading to fast development cycles than traditional hardware description languages (HDLs) like Verilog or VHDL.

- Fast Prototyping: HLS enables rapid prototyping and iteration, allowing designers to test and modify designs quickly. A typical bit-accurate algorithm can be compiled and validated with SYCL in under 1 minute, allowing for considerably fast design iterations than RTL simulations.

- Error Reduction: Higher-level abstraction can reduce the chance of low-level errors, leading to more robust designs.

- Efficient Resource Management: HLS can optimize hardware resources, resulting in more efficient designs, especially regarding area and power consumption.

- Enhanced Design Exploration: HLS provides capabilities to explore different architectural choices automatically, helping designers find the optimal balance between performance, area, and power consumption.

- Improved Code Reusability: High-level code can be more easily reused across different projects, reducing the effort needed to create new IP cores.

- Automatic RTL Verification: IP blocks generated by HLS include RTL test benches, with stimuli and results automatically extracted from the source code, to create and automatically verify the IP using RTL simulation.

- Seamless Integration: Intel’s implementation of HLS, oneAPI, integrates seamlessly with Quartus manually or through Platform Design, allowing smooth transitions between design, simulation, and synthesis.

Using oneAPI and HLS for IP development in Quartus is a game-changing approach. It simplifies the process and enhances productivity, making it an essential strategy for any tech business looking to stay competitive in today's market.

A wealth of resources is available if you're ready to investigate the oneAPI flow or start developing with oneAPI. These include:

- Self-starting videos to guide you through the entire flow from tool installation to running your new RTL IP on an FPGA.

- Guides on easily converting existing C and C++ algorithms to SYCL.

- FPGA-focused oneAPI documentation.

- Over 40 tutorial examples on common performance modeling techniques.

- Design reference examples from multiple market segments.

These resources will enable you to quickly evaluate oneAPI for IP development and ramp.

Self-Starting with oneAPI Learning Videos

The quick way to use oneAPI for IP development in Quartus is to visit Channel Intel on YouTube.

These short oneAPI FPGA videos explain everything from installing the tools through debugging, synthesis, and optional in-depth analysis of the RTL waveforms. You will learn how oneAPI is used to quickly generate optimized RTL IP and see how it automatically creates the RTL testbench and software drivers required for optional control via a CPU.

- Learn how to install oneAPI for FPGA development with Intel Quartus on a Linux or Windows operating system, launch oneAPI, and run and debug a code sample.

- Learn how to capture your Quartus design IP in SYCL, quickly emulate it to confirm functional correctness, and invoke the debugger for detailed analysis.

- Understand how to generate RTL IP for Quartus using oneAPI and review the synthesis reports. You will learn how to review the design performance, and area resources and how to perform bottleneck analysis with the loop and system viewers.

- Learn how to verify that the RTL generated by oneAPI matches the pre-synthesis SYCL source results and understand how to perform an optional detailed analysis of the RTL waveforms.

- A complete SYCL-to-FPGA example. See how to design an IP with SYCL and export it to Platform Designer for use in your Intel Quartus Pro projects. You will learn how to control the IP from a CPU via the Control Status Register and how to run it on an Intel FPGA board.

Once you understand the flow, you can get hands-on experience with over 40 tutorial examples.

Get Productive with oneAPI through Tutorial Examples

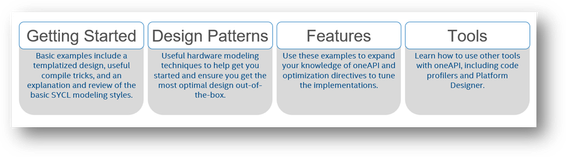

Tutorial Examples demonstrate how FPGA hardware is easily modeled with SYCL and how optimization directives are used to implement specific hardware behaviors not inferred by the source code, such as IO port implementations and protocols. The examples are grouped into four categories.

- Getting Started examples demonstrate the basics of running oneAPI for FPGA development. These examples include the FPGA Compile Sample, which shows the same design model with different styles to highlight the support for both functor and lambda SYCL modeling styles and the benefits of Universal Shared Memory (USM) support.

- With the Design Pattern examples you will learn how to easily model and incorporate common design patterns into your IP models, including double and N-way buffering, triangular loops, on-chip memory caches, zero-copy data transfers, etc.

- Multiple feature examples are provided to help learn oneAPI optimization techniques such as loop fusion, pipes, optimization targets, and stall enable. This category also introduces designing with arbitrary precision and fixed-point bit-widths in SYCL.

- Learn how to use additional tools with oneAPI, especially the detailed tutorial on working with Platform Designer.

The tutorial examples will enable you to increase your productivity quickly: Use the template examples to get started quickly with a productive workflow, quickly understand what SYCL modeling style suits your requirements or personal style, copy useful modeling constructs directly from working code into your IP, and learn to use other tools to improve your overall productivity.

Learn to push for Performance by using oneAPI Reference Examples.

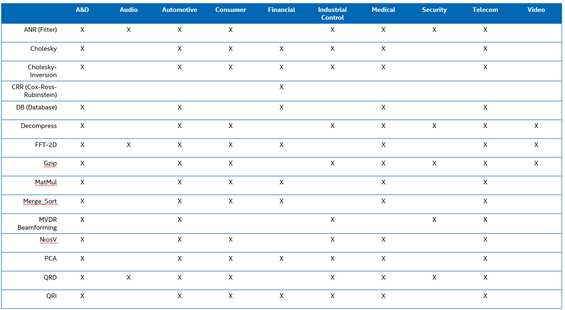

When it’s time to grow your design into hardware IP that delivers high performance and small area, complete Design Reference Examples for multiple market segments are provided. Note that these examples may apply to additional market segments other than those shown.

The reference designs provide starting points for your complex and performant IP. A complete set of FPGA-focused documentation is provided as you grow your design example using the good practices and examples provided.

Comprehensive Unified oneAPI FPGA Handbook

The Intel oneAPI FPGA Handbook is an excellent resource for developers exploring the world of oneAPI FPGA development. Its comprehensive layout provides a clear roadmap for both new and experienced developers.

The handbook starts with an Introduction To FPGA Design Concepts. This section is vital for developers starting in FPGA programming as it describes FPGA hardware concepts and how the Intel® oneAPI converts your SYCL code into an FPGA application.

Next, it delves into the Intel oneAPI FPGA development flow. This section is subdivided into numerous parts, covering everything from an overview of the FPGA development flow to the functional correctness verification of your kernel. Each sub-section provides detailed guidelines and techniques for the different stages of development, ensuring a comprehensive understanding of the FPGA development process.

- Intel oneAPI FPGA Development provides an overview of the FPGA development flow.

- Defining a Kernel for FPGAs provides coding guidelines for your kernel

- Optimizing Your Kernel provides an overview of methods to optimize your kernel performance and the parts of your kernel code that you can examine to improve performance.

- Analyzing Your Design provides information about tools and techniques to analyze your kernel design without running the kernel on hardware. Use these tools and techniques to determine what parts of your kernel you can optimize or adjust before you compile your kernel for FPGA hardware.

- Debugging and Verifying Your Design provides information about tools and techniques you can use to verify the functional correctness of your kernel.

- Integrating Your RTL IP Core Into a System provides information about integrating an RTL IP core generated by the Intel® oneAPI DPC++/C++ Compiler into a larger FPGA design.

The Optimization Areas segment discusses specific areas for optimization like Loops, Pipes, and Memory Operations. This is an invaluable resource for developers looking to maximize the performance of their FPGA applications.

The handbook also addresses using libraries in your kernel and generating libraries from your kernel, a crucial aspect that developers can sometimes overlook.

To ensure a well-rounded understanding, the guide includes Additional Considerations when developing your IP, providing an extra layer of detail to the FPGA development process.

Finally, the handbook includes a reference material section with a list of compiler optimization flags, attributes, pragma, and extensions. This is an excellent quick reference for developers on FPGA-specific attributes, pragmas, and variables, making the development process smoother and more efficient.

Get Started Today

Download Intel® oneAPI Base Toolkit today, and use the resources listed in this blog post to move your IP development to the next level of enhanced productivity. The following additional resources provide further help and guidance.

Additional Resources

Be sure to check out other resources on using oneAPI with FPGAs:

oneAPI and SIMD Instructions are a natural fit for database acceleration on Intel FPGAs

oneAPI and Agilex deliver X233 over CPUs

FPGA Provides a 95% decrease in latency vs. CPU

FPGA Advantages for AI inferencing

FPGA Power and Performance Benefits over GPUs

Free DPC++ book to learn SYCL (DPC++ is the Intel implementation of the SYCL specification)

(1) https://www.dell.com/en-us/blog/fpgas-vs-gpus-tale-two-accelerators

(2) https://www.youtube.com/watch?v=Rlh0JFUWkmI

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.