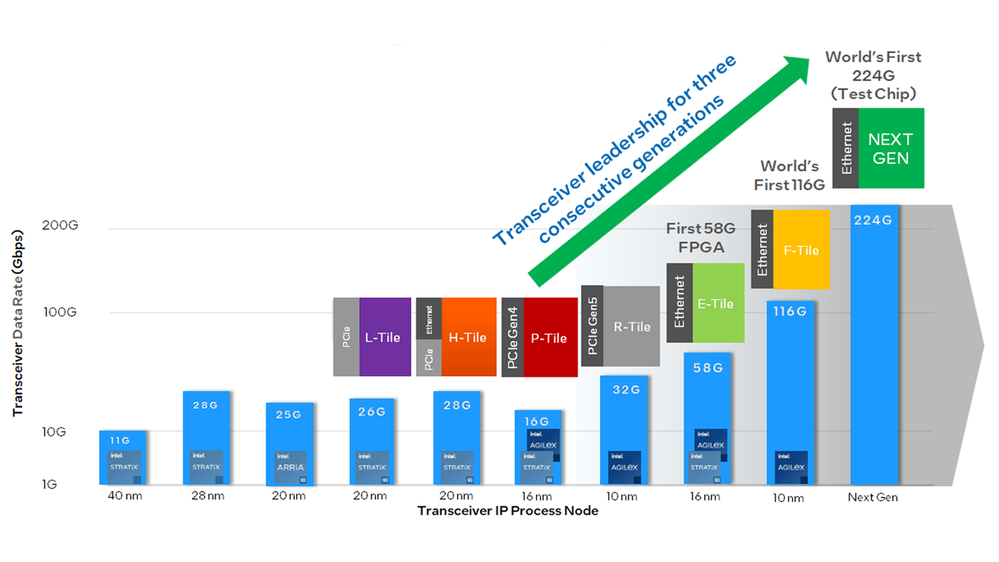

High-speed serial transceivers quickly became a foundational FPGA component when they appeared more than 20 years ago and have grown increasingly important as their bandwidth has exploded. These high-speed transceiver designs are sufficiently flexible and configurable to directly implement a very wide variety of standard digital serial communications protocols including Ethernet, PCI Express (PCIe), Compute Express Link (CXL), serial digital interface (SDI), and so on. Intel has long had a leadership position in the development of high-speed serial transceivers, as shown in Figure 1.

Figure 1: Transceiver Technology Leadership in Intel FPGAs

Figure 1 shows that high-speed transceiver data rates have risen from 10 Gbps at the 40 nm process node to 116 Gbps with the most advanced Intel process node for FPGAs, and Intel has already demonstrated a 224 Gbps high-speed transceiver test chip, which signals where FPGA transceiver technology is headed.

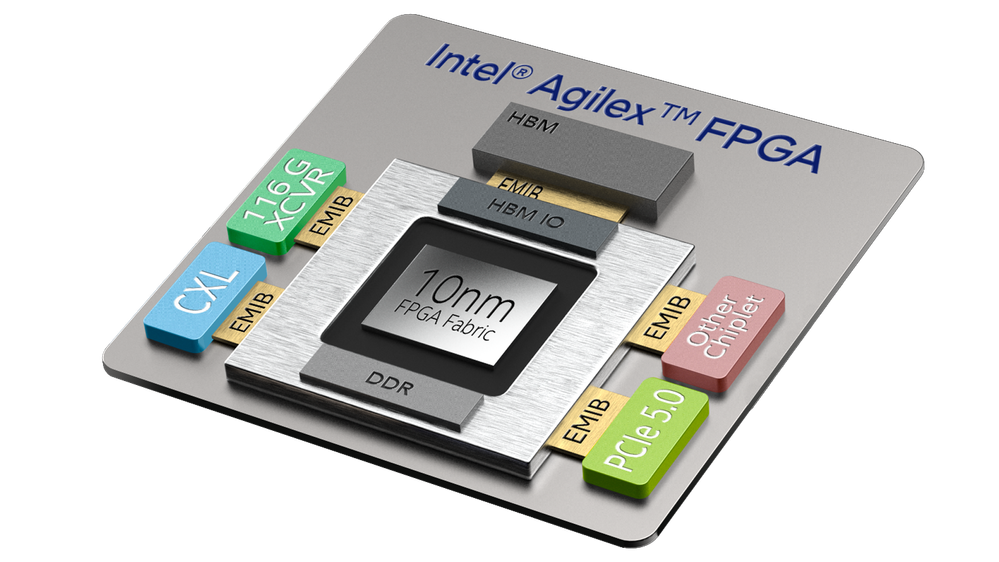

The most recent Intel® FPGA families including the Intel® Agilex™ and 10 FPGAs and SoC FPGAs incorporate separate chiplets, which Intel calls “tiles,” to implement high-speed transceivers. This tile-based approach to FPGA construction permits great flexibility in developing broad device families with many capabilities in an expedient and cost-effective manner.

Figure 2 shows the internal construction of an Intel Agilex FPGA. In Figure 2, five chiplets surround a central semiconductor die containing the Intel Agilex FPGA’s programmable logic fabric and other logic circuits including DDR and High Bandwidth Memory (HBM) controllers. Four of the five chiplets are labeled “116G XCVR,” “CXL,” “PCIe 5.0,” and “Other Chiplet.” The fifth chiplet, marked “HBM,” is actually a chiplet stack containing several gigabytes of HBM DRAM.

Figure 2: Intel Agilex FPGA

Although marked with different names for high-speed serial protocols, the “116G XCVR,” “CXL,” and “PCIe 5.0” functions . Intel developed these tiles to provide the fastest serial transceiver capability possible, whether it’s 4

Each F-tile transceiver chiplet adds 20 high-speed transceiver channels to the FPGA. Of the 20 high-speed transceivers on each F-tile, there are four FHT transceivers, each capable of running as fast as 116 Gbps using PAM4 modulation, and there are twelve FGT transceivers, each capable of running at 58.125 Gbps using PAM4 modulation. In aggregate, these 20 high-speed transceivers deliver more than 700 Gbps of data bandwidth. For Intel Agilex I-Series and M-Series FPGAs with a maximum of four F-tiles, the total high-speed serial bandwidth exceeds 2.4 Tbps. Intel Agilex I-Series FPGAs are available with as many as six F-tiles, which support a maximum aggregate bandwidth of 4.32 Tbps¾in one FPGA!

Intel has just published a 5-minute video that demonstrates the Intel Agilex FPGA family’s high-speed data-transfer capabilities enabled by the F-tiles’ high-speed transceivers. The demo uses the Intel SuperLite IV IP, which is a low-overhead serial streaming protocol. The SuperLite IV IP harnesses the F-tile’s PHY Direct feature, which has a PMA Direct mode that bypasses the F-tile’s media access control (MAC) and physical coding sublayer (PCS) hard IP block. Bypassing these elements in the high-speed transceiver minimizes latency, which makes the SuperLite IV protocol an excellent choice for chip-to-chip, board-to-board, and backplane applications.

The demo uses the FGT transceivers on the F-tile, running at 53 Gbps with PAM4 modulation, and achieves an aggregate bandwidth greater than 2.4 Tbps in an Intel Agilex I-Series FPGA with four F-tiles. Watch the demo video.

For more in-depth information about the F-tile’s capabilities, see the “F-tile Architecture and PMA and FEC Direct PHY IP User Guide.”

For more information on the SuperLite IV IP and protocol, click here.

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.