- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have gone through the UG :Intel® Arria® 10 DisplayPort IP Core Design Example User Guide

UG-20075, and example design

In this it uses FPLL and stores calibrated link rates for different speeds. and while changing from one speed to other calibration is not required.

My query is

1)can use ATX PLL instead of FPLL ?

2)Does ATX Pll supports storing link rate feature ? without using Multiple Reconfiguration Profiles!

Regards,

Rajesh

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

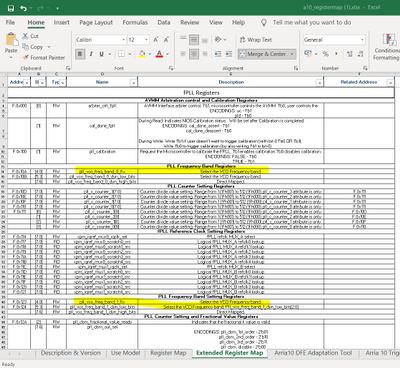

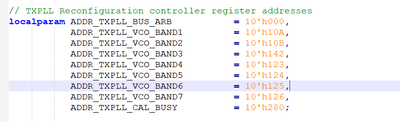

In display port design for FPLL is used, which having registers to store the frequency band, the similar registers are not available for ATX PLL.

SNAPSHOT FROM A10 register map excel sheet.

I need to figure out whether i can use the existing logic from display port for switching speed when i use ATX PLL without re calibrating after changing speed?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

These registers are available in FPLL section, and these are used for storing link rate and load back the link rate,

can these registers will work for ATX PLL too ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page