- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm looking to implement 1G/10GBASE-KR in an Arria 10SX. I should be able to use the native MAC+ PHY and access them through Linux drivers but I've not found any available for the LL MAC. Are there available drivers for the MAC IP?

In the same vein, two follow up questions:

1) Am I able to generate the internal clocks necessary for the speeds or do I need to provide an external reference clock for the x1 lane required.

2) My connection from the SOC to the backplane should be direct. Is this also correct?

My examples have been loopback only and I'd like to move to implementing multiple 1G/10G with I believe the native HPS EMAC cannot do (nor can it meet low latency requirements for network stacks).

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can we implement 1G/10GBASE-KR in an Arria 10SX?

Yes.

Will I able to use the native MAC+ PHY and access them through Linux drivers?

MAC + PHY is implementable.

Do we have any available for the LL MAC?

MAC is LL MAC only for A10

Are there available drivers for the MAC IP?

For Drivers Check this link https://rocketboards.org/foswiki/Projects/Stratix10SoCDesignExampleFor10GbeWithIEEE1588PTPCapability212

I think the same design of S10 SoC maybe you can try porting to A10 SoC to test it. C application would be the same and driver too, only HPS changes from A53 to A9 as in ARRIA 10.

Also, Will you be able to generate the internal clocks necessary for the speeds or do you need to provide an external reference clock for the x1 lane required?

Internal clocks can be generated to whichever frequencies but its not recommended for transceiver applications as the jitter performance of PLLs are not as good as external clock sources.

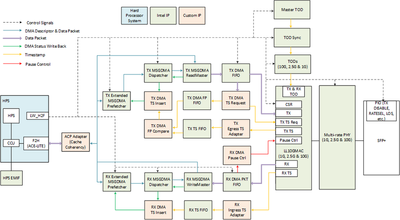

Also, In above S10 reference design block diagram u can see clocks are coming from external and supplied.

Is my connection from the SOC to the backplane should be direct?

Directly SoC cannot talk to SFP, it needs intermediate blocks.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. This is all helpful. In this implementation an SFP would not exist but would connect to a copper backplane. I assume that is fine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you

Kshitij Goel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page