- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

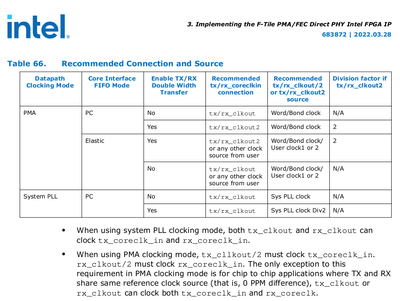

The FGT is configured using System PLL to have the same clock at the TX and RX.

The user guide says both clocks are same.

When using system PLL clocking mode, both tx_clkout and rx_clkout can clock tx_coreclk_in and rx_coreclk_in .

Both rx_clkout and tx_clkout are generated clocks.

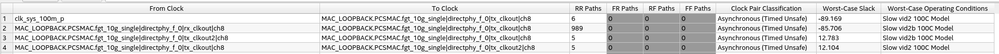

Nevertheless, I get lots of CDC timing failures between endpoints crossing them.

Some of them come from the IP itself:

12.783 MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|waddr_g_completed[1] MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|sr0|resync_chains[1].synchronizer_nocut|din_s1

12.790 MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|waddr_g_completed[2] MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|sr0|resync_chains[2].synchronizer_nocut|din_s1

12.795 MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|waddr_g_completed[4] MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|sr0|resync_chains[4].synchronizer_nocut|din_s1

12.815 MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|waddr_g_completed[3] MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|sr0|resync_chains[3].synchronizer_nocut|din_s1

12.825 MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|waddr_g_completed[0] MAC_LOOPBACK.PCSMAC.fgt_10g_single|directphy_f_0|dphy_sip_inst|persystem[0].ccg.ccg|sr0|resync_chains[0].synchronizer_nocut|din_s1

- Are they really one unique clock?

- Is it a bug that Quartus doesn't consider them as a single clock?

- How about the missing constraints?

Regards,

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please share your project to replicate the issue.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please share your project to replicate the issue.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As, We do not receive any response from you to the previous reply that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page