- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Community,

I'm working with the FFT IP core provided by the Intel in Quartus.I want to use the same module to implement FFT and IFFT.For example,

FFT IP CORE SETTING:

Device:Cyclone IV E

Length:64

Data Flow:Variable Streaming

Data Representation: Floating Point

Direction:Bi-directional

First, I first sent the tested data into the FFT module, where the inverse signal was at a low level. Then, after FFT operation, I sent the output data into the module as the input data of IFFT, and changed the inverse signal into a high level.But the timing of the output is not consistent with my expectations.

Can you help me what are the other things i should see to find out this problem?

Thanks for reading.

- Tags:

- fft

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you observe some issue with the FFT to iFFT interface. Just would like to check with you on the following:

- Would you mind to further elaborate on the timing not meeting your expectation observation? Some screenshot of docx would be helpful.

- Are you observing this in Modelsim simulation or hardware?

- If it is hardware, it is recommended for your to create simple test design and simulate with Modelsim to isolate potential functional issue prior to hardware testing.

- What is the Quartus version that you are using?

- Have you tested with other data format ie try start with fixed point

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus version:Quartus 13.1

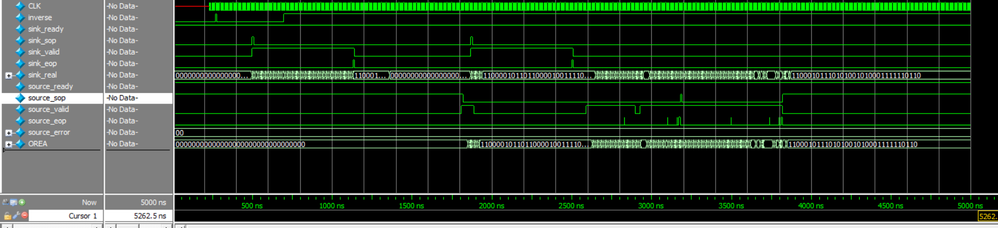

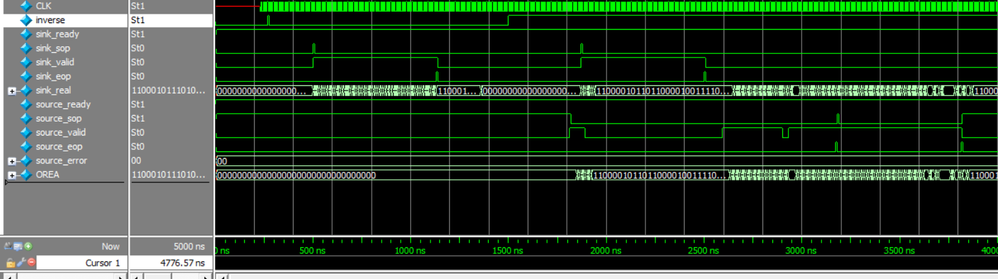

I have done the simulation with the Modelsim , and the test results are as follows

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For your information, as I search through the web, I found a design in Design Store which might be helpful for your reference:

https://fpgacloud.intel.com/devstore/platform/17.1.0/Pro/cyclone-10-gx-fft-to-ifft-with-natural-input-and-output-order-using-cosine-data-example-design-171/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the update. Would you mind to further elaborate on your simulation waveform? I observe from the waveform that the inverse seems to be toggling half way when the input data is still streaming into the FFT. Not sure if this is something expected?

Just wonder if you have had a chance to look into the example design which I share previously?

To facilitate your debugging, it would be great if you could create simple test design with test data (ie sine wave) -> FFT -> iFFT -> output data (sine wave with reduce magnitude) in your simulation. With this, you could cross check again the output data of iFFT to see if it is still following the same shape of the input data with reduced magnitude.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply.

My idea is whether it is possible to use only one module to realize FFT and IFFT operations, so I only use one IP core to do the following test,

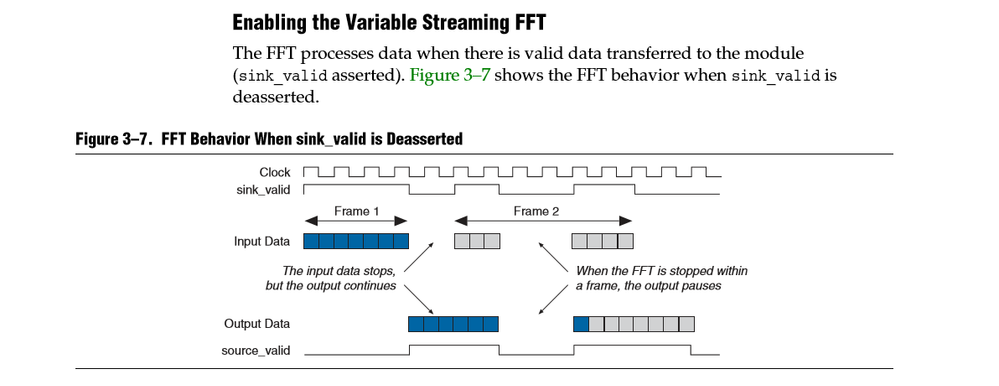

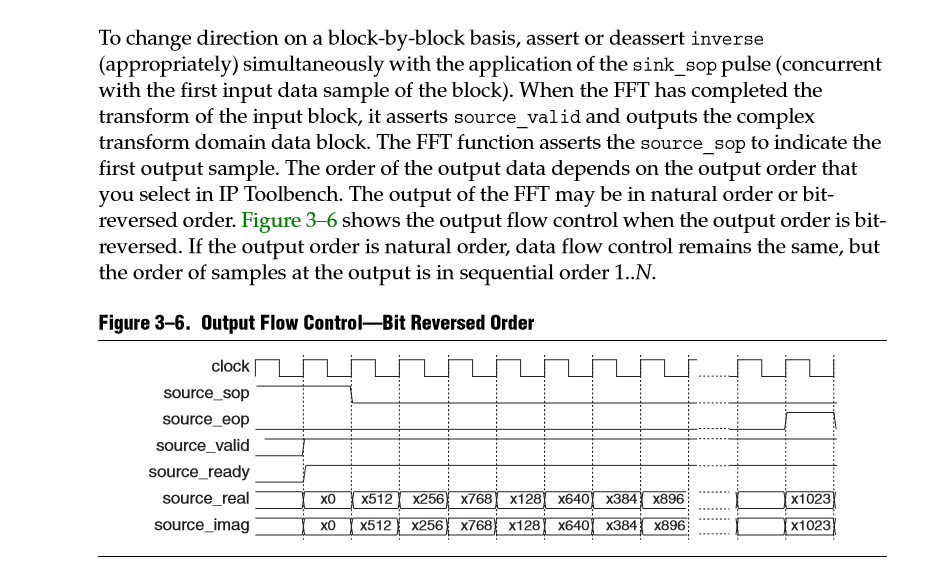

According to FFT data manual, FFT operation is performed on 64-point sinusoidal data, and the inverse is equal to 0;Then wait for FFT to output the data, and send the output data source_real and source_imag into the same module for IFFT operation, at which time inverse=1.But the source_valid timing, source_real and source_imag seem to be wrong.

What is the reason for this problem? Thank you in advance for your help

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As you said, it will work just fine.However, because my design needs too many resources to use two modules to implement FFT and IFFT, I consider using a single module to implement FFT and IFFT.Using a single module to implement FFT and IFFT is, in my opinion, the same as the continuous input data into the FFT module, only the inverse signal changes.I think the output sequence is as follows,

Is that not a viable idea?Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your help, I have another question, change the inverse processing direction, which means after the FFT transformation, wait until all the data is out before you can change the inverse direction?My understanding should be that the next sink_sop assertion can be changed, if so, then my idea should be achievable;If I don't understand that, as you said, I need to wait for all the FFT data to be output before I can change the direction of the inverse, then I will do what you said.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you. I'm trying to do that.

Thanks again for your help.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page