- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

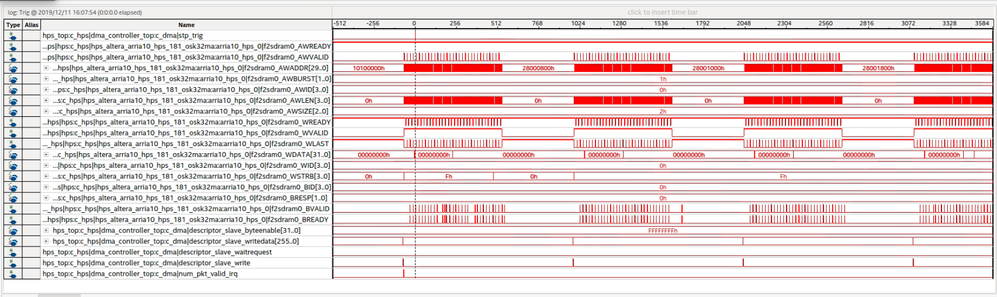

I'm trying to achieve the aforementioned transaction in a 10AS066H3F34I2SG device, but I'm experiencing erroneous operation on the f2sdram AXI interface. On the following picture three complete transaction is shown and can be seen, that in the first write burst all 4 bits of WSTRB signal goes low before finishing all writes (at around clock cycle 512).

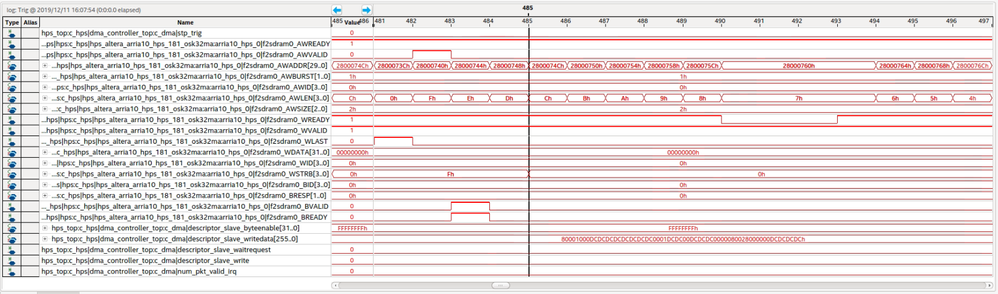

Here I have a zoomed picture as well:

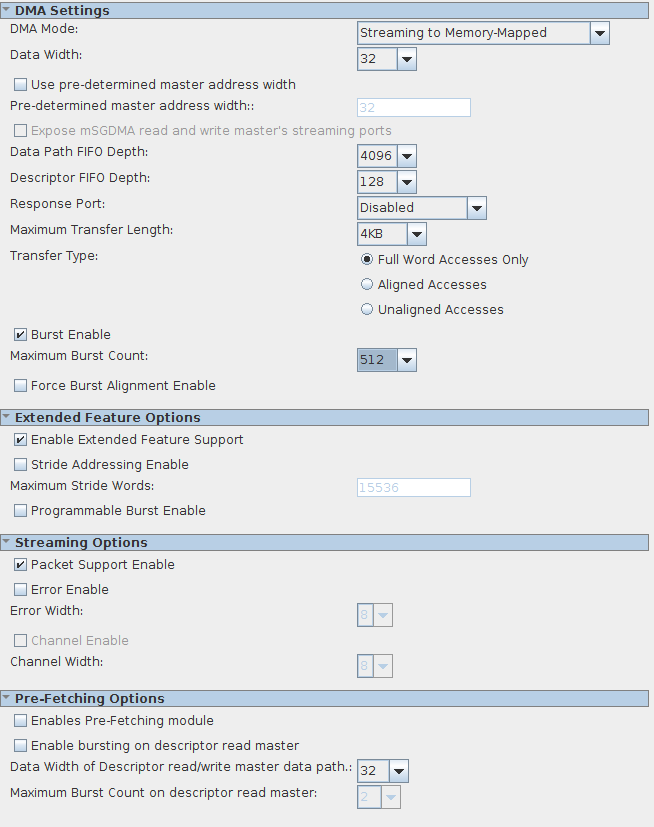

The MSGDMA module is created in Platform Designer 18.1 Build 625 with the following settings (and all other reasonable settings have already been tried out also resulting in wrong behaviour):

The descriptors are generated inside the FPGA, written a couple of clock cycles after the Avalon St end-of-packet gets asserted (let me mention another error here: according to this the sop shall be asserted along with the first valid data, but doing so the MSGDMA then will skip writing that first channel data). In the extended descriptors I create the 'GO' and 'End on EOP' bits are set to '1'. The 2nd picture shows a descriptor_slave_writedata with all unused data bytes set to 0xDC

As the MSGDMA documentation doesn't say anything about the write order of data packet and descriptors, or how the end on EOP works, different methods have been tried (length field set to MAX with end on EOP enabled, length field set to 2048 with end on EOP disabled, etc.), none of them resulted in the desired operation.

Thank you for your help in advance,

G. Ivanyi

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check the following examples for msgdma:

https://fpgacloud.intel.com/devstore/?search=msgdma.

Please let me know if you are looking for something else.

Regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page