- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

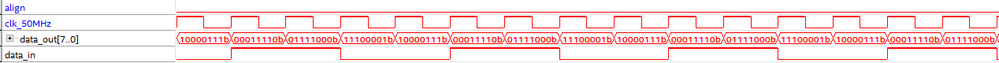

I am using Max10 and included Soft LVDS IP core for data transmission and reception. For link training I sent 8'h0F. Now, the data at LVDS Rx slips every clock cycle.

General:

Power Supply Mode: Single Supply (for 10M16SAE144I7G)

Functional Mode: Rx

No. of channels: 1

SERDES factor: 8

PLL Settings:

Use external PLL (checked)

Receiver Settings:

Enable bitslip mode (checked)

Bitslip rollover value: 1

I have also tried to use internal PLL in which case the the bitslip occurs at random intervals. Now how can I fix this issue?

- Tags:

- Programmable Devices

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SMS,

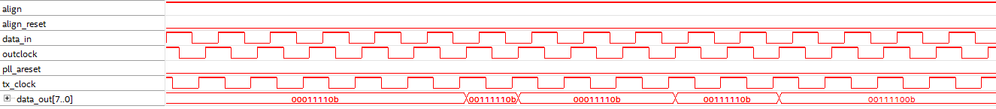

It is a strange behaviour - in case align is stable you shouldn't get bitslip as it is on first figure.

You could attach your project in order for community to check it.

--

Best regards,

Ivan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SMS,

I quickly checked your project and I can say that you should begin with a creation of constraint file (sdc).

You should start with create_clock command, FE create_clock -name {I_ADC_FCO} -period 20.000 -waveform { 0.000 10.000 } [get_ports {I_ADC_FCO}]

After that and after successful timing analysis you should test if your design works.

--

Best regards,

Ivan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page