- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are trying to interface some high speed protocol devices with Stratix 10 SoC dev kit @20gbps.

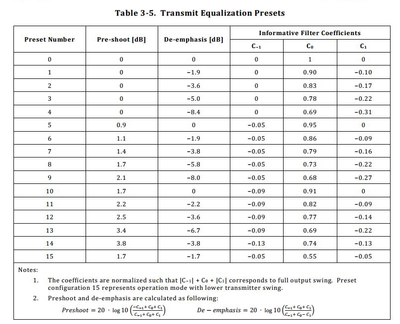

The protocol expects the Transmit presets as shown below.

Also, I downloaded the pre-emphasis estimator for Stratix 10 from below link.

My question is how to support the protocol specific presets with the help of VOD, "1st Pre-Tap Pre-Emphasis" & "1st Post-Tap Pre-Emphasis" of the stratix 10 transceivers.

With regards,

HPB

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi HPB,

As I understand it, you have some inquiries related to the TX Analog PMA settings in the S10 Native PHY to meet your target protocol's requirement. As I look at the screenshot that you share, sorry as I am not sure how to translate the table into the exact setting in the Native PHY. As a workaround, you can try to look through the TX/RX PMA analog mode rules at the Analog PMA Settings tab to see if you can find your target protocol.

If not, you might need to explore into how to map the table's value into our S10 Native PHY settings. Sorry for the inconvenience.

By the way, what is the specific protocol that you are targeting?

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are targeting USB4 protocol.

With Regards,

HPB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the inconvenience. I might have overlooked your latest response.

Thanks for your clarification that you are targeting USB4. As I understand it from the S10 L/H-Tile user guide, seems like there is no specific information about USB4 protocol. In other words, there is no formal support or characterization done for USB4 protocol. This could explain why there is no ready preset on this in the Native PHY.

As a workaround, you would need to perform your own evaluation on the right set of PMA analog settings to work with your target protocol as suggested in my previous note. Sorry for the inconvenience.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, it has been some time since I last heard from you. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page