- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using the LPDDR3 controller on an Arria 10.

Question 1: Is there a fixed phase relationship between "pll_ref_clk" and "emif_usr_clk"? Assume they have the same period.

Question 2: If I issue a burst read of, say, 0x40 transfers and the sequence crosses the end of the currently selected bank & row ("page"), does the controller close the page and open the next and continue? Or does it recycle down to the locations at the bottom of the current page?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KCMurphy,

"1. If the clock skew (phase relationship) is fixed, is it the same from reset to reset and in each device, and if possible, what is it? Normally a PLL has a skew parameter but for this IP that parameter is not visible. Other parts of the design MUST use the reference clock as the output of a PLL (such as the EMIF user-clock) is generally not stable enough."

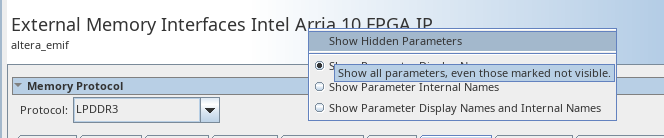

There are some hidden parameter inside the IP parameter GUI.

You can view the hidden parameter by right-click on IP name and click show hidden parameter.

"2. In simulation, it appears that if the controller is set for CHIP-ROW-BANK-COLUMN, the controller changes the BANK. If set for CHIP-BANK-ROW-COLUMN it changes the ROW. IS this accurate?"

Yes it's accurate. It's control the bank/row switching whether row to bank or bank to row.

It is the address ordering setting where the controller will manage the mapping between Avalon address and memory device address.

Regards,

Adzim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KCMurphy,

Thank you for submitting your question in Intel Community.

I'm Adzim, application engineer will assist you in this thread.

Please find my answer below.

"Question 1: Is there a fixed phase relationship between "pll_ref_clk" and "emif_usr_clk"? Assume they have the same period."

I would say yes if they have same period.

"Question 2: If I issue a burst read of, say, 0x40 transfers and the sequence crosses the end of the currently selected bank & row ("page"), does the controller close the page and open the next and continue? Or does it recycle down to the locations at the bottom of the current page?"

From my understanding on sequential burst operation, it's will open the bank first and close it after the operation is done. In the middle of operation, the bank should not be closed.

You can refer to this document for burst example: https://www.intel.com/content/www/us/en/docs/programmable/683609/21-3/memory-mapped-burst-host-example.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. If the clock skew (phase relationship) is fixed, is it the same from reset to reset and in each device, and if possible, what is it? Normally a PLL has a skew parameter but for this IP that parameter is not visible. Other parts of the design MUST use the reference clock as the output of a PLL (such as the EMIF user-clock) is generally not stable enough.

To interface the two clock domains, it is really handy to know the phase relationship, or at least to know if it is the same in each activation of the device.

2. In simulation, it appears that if the controller is set for CHIP-ROW-BANK-COLUMN, the controller changes the BANK. If set for CHIP-BANK-ROW-COLUMN it changes the ROW. IS this accurate?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KCMurphy,

"1. If the clock skew (phase relationship) is fixed, is it the same from reset to reset and in each device, and if possible, what is it? Normally a PLL has a skew parameter but for this IP that parameter is not visible. Other parts of the design MUST use the reference clock as the output of a PLL (such as the EMIF user-clock) is generally not stable enough."

There are some hidden parameter inside the IP parameter GUI.

You can view the hidden parameter by right-click on IP name and click show hidden parameter.

"2. In simulation, it appears that if the controller is set for CHIP-ROW-BANK-COLUMN, the controller changes the BANK. If set for CHIP-BANK-ROW-COLUMN it changes the ROW. IS this accurate?"

Yes it's accurate. It's control the bank/row switching whether row to bank or bank to row.

It is the address ordering setting where the controller will manage the mapping between Avalon address and memory device address.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for #2. As for #1, the exposed "hidden parameters" do not include the PLL phase angle in any clear way.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KCMurphy,

Is there any question regarding to this topic?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page