- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

can anyone help me out with this

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share more information?

Version of tools and Full name of the IP used in you design with simulation images.

If possible do share project files.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raj

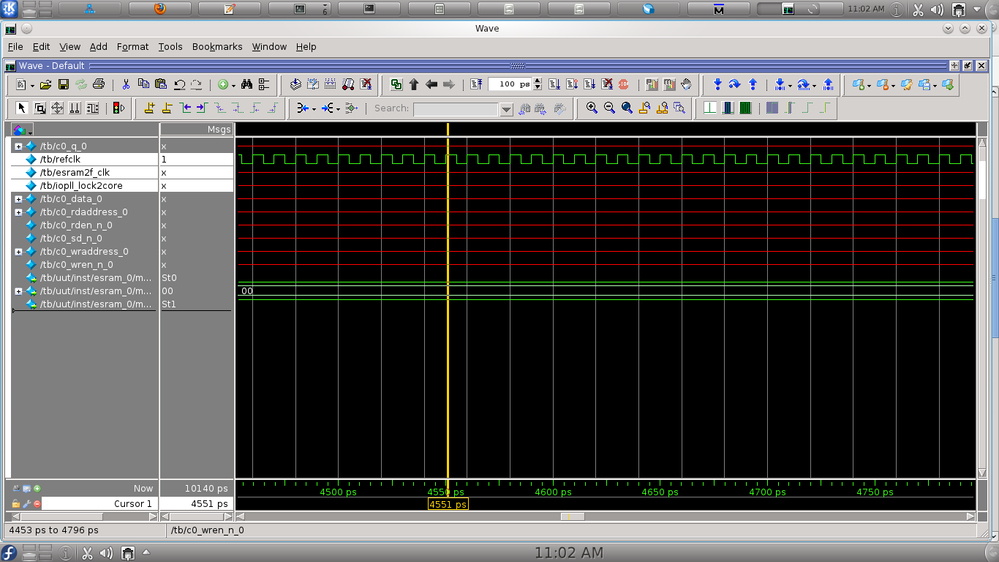

am using 18.1 quartus tool and IP name is "ESRAM" here am attaching the project files and the simulation waveform capture,while generating the IP core i configured the 'refclk' as 100Mhz and output clk as 500Mhz but when am trying to drive the reflck from the testbbench am able to get the refernce clk but am unable to generate the output core clk and lock signal , is there anything i have to drive from the testbench??

Abhishek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi few points to add

am using stratix 10 MX board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raj is there any updated info regarding the "esram ipcore" ,we need simulation to be tested for our further integration.Could you please give me some info regarding the issue ASAP.

Regards

Abhishek

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page