- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Team,

I am checking the design with ddr3 interface, nios processor and other interfaces also in cyclone v gx device(5CGXFC5C6F27C7). I have given memory clock as 400 Mhz(ddr3 ip parameter setting) and uses afi_clock(200 Mhz) to connect the clock of other interfaces.

pll_clock of ddr interface is 50 Mhz. connected from the osciallator in the board.

Nios processor also connected with afi clock only (200 Mhz)

For this design , i am getting pll_afi_clock setup time violation.

i have attached the timing report.

PLease give solution for this.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The setup violations showed in the report are all asynchronous path. You can use 'set clock group' constraint to eliminate the relationship between 'inst|ddr3|pll0|pll_dq_write_clk ' and 'dqs_n[3]_OUT'.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ting,

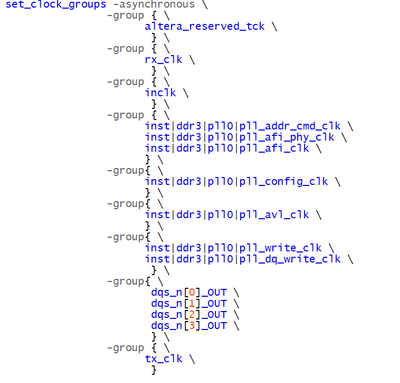

I have added constraint for the clocks like you have mentioned, but still facing the timing violation error:

could you please give suggestions whether this constraints are okay?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

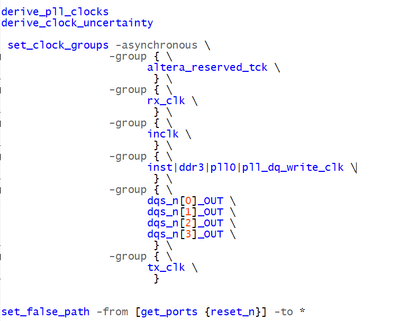

You don't need to constraint all the clocks, just apply it to the clocks of asynchronous path( the launch and latch clock ).

BTW you can try to apply the following constraint:

'derive_pll_clocks'

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I have tried with derive_pll_clock also. but still facing timing violation issue.

do i miss anything?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You mean the same violation still exits? Could you show the violation in the timing analyzer which is better to view.

BTW why you put the altera_reserved_tck in the group? I think you don't need to constraint it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

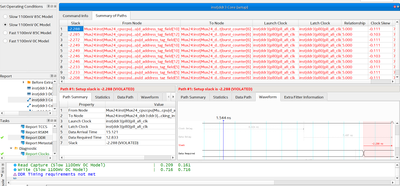

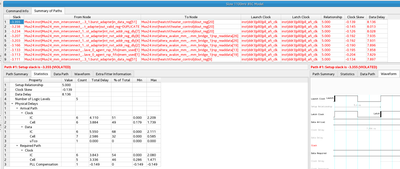

for better view, i have attached the screenshot of violation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There are also synchronization path violation. Could you please provide your project for further analysis.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i have attached the project archive with this response. Please let me know if you have any query on this. please give solution for this violation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there, I can't open timing analyzer with the project you provided. Could you provide the project which has completed the compilation process?

Please provide all the files of the project, and you can exclude you RTL(.v file) for confidentiality.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok , i will send the project files which is compiled within today

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

sorry for the delay response. i will send the project archive today. please reopen the ticket.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try reduce the number of logic levels to 2-3 by adding pipeline register (this will add latency in your design).

As higher logic level will increase delay on the critical path.

You may checkout this video on @16.49 minute marks

https://www.youtube.com/watch?v=UGGkKZylJBo

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok i will check this and let you know

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you able to close timing?

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

No still i am working on it..but for me timing violations are showing within the ip files. i cant modify the rtl path , so need assistance for this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

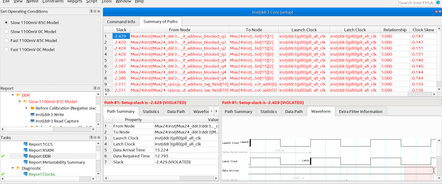

Hi there, what violation you get, could you please share the path in timing analyzer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am getting timing violation for these path

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please provide your project (.qar) for investigation. You can remove all RTL files for confidentiality.

Thanks a lot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have already shared the project archive in this query chain. Please check this project file is ok.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page