- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

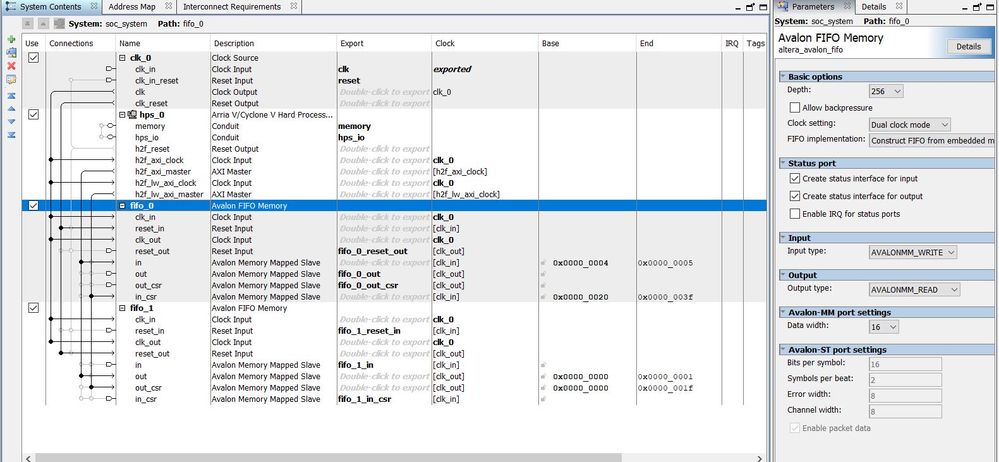

what is "fifo_out_csr_address" input in Avalon FIFO Memory ip?

Link Copied

3 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Is there any possible screenshot of the system design that show that signal for better investigation

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the qsys system picture attached. and the module instantiation of qsys system. You can see (fifo_0_out_csr_address) and (fifo_1_in_csr_address). Just wana know what are these ports? and these are input ports.

module soc_system (

input wire [2:0] fifo_1_in_csr_address, // fifo_1_in_csr.address

input wire [2:0] fifo_0_out_csr_address, // fifo_0_out_csr.address

input wire clk_clk, // clk.clk

output wire [15:0] fifo_0_out_readdata, // fifo_0_out.readdata

input wire fifo_0_out_read, // .read

input wire fifo_0_out_csr_read, // .read

input wire [31:0] fifo_0_out_csr_writedata, // .writedata

input wire fifo_0_out_csr_write, // .write

output wire [31:0] fifo_0_out_csr_readdata, // .readdata

input wire fifo_0_reset_out_reset_n, // fifo_0_reset_out.reset_n

input wire [15:0] fifo_1_in_writedata, // fifo_1_in.writedata

input wire fifo_1_in_write, // .write

input wire fifo_1_in_csr_read, // .read

input wire [31:0] fifo_1_in_csr_writedata, // .writedata

input wire fifo_1_in_csr_write, // .write

output wire [31:0] fifo_1_in_csr_readdata, // .readdata

input wire fifo_1_reset_in_reset_n, // fifo_1_reset_in.reset_n

inout wire hps_io_hps_io_sdio_inst_CMD, // hps_io.hps_io_sdio_inst_CMD

inout wire hps_io_hps_io_sdio_inst_D0, // .hps_io_sdio_inst_D0

inout wire hps_io_hps_io_sdio_inst_D1, // .hps_io_sdio_inst_D1

output wire hps_io_hps_io_sdio_inst_CLK, // .hps_io_sdio_inst_CLK

inout wire hps_io_hps_io_sdio_inst_D2, // .hps_io_sdio_inst_D2

inout wire hps_io_hps_io_sdio_inst_D3, // .hps_io_sdio_inst_D3

inout wire hps_io_hps_io_usb1_inst_D0, // .hps_io_usb1_inst_D0

inout wire hps_io_hps_io_usb1_inst_D1, // .hps_io_usb1_inst_D1

inout wire hps_io_hps_io_usb1_inst_D2, // .hps_io_usb1_inst_D2

inout wire hps_io_hps_io_usb1_inst_D3, // .hps_io_usb1_inst_D3

inout wire hps_io_hps_io_usb1_inst_D4, // .hps_io_usb1_inst_D4

inout wire hps_io_hps_io_usb1_inst_D5, // .hps_io_usb1_inst_D5

inout wire hps_io_hps_io_usb1_inst_D6, // .hps_io_usb1_inst_D6

inout wire hps_io_hps_io_usb1_inst_D7, // .hps_io_usb1_inst_D7

input wire hps_io_hps_io_usb1_inst_CLK, // .hps_io_usb1_inst_CLK

output wire hps_io_hps_io_usb1_inst_STP, // .hps_io_usb1_inst_STP

input wire hps_io_hps_io_usb1_inst_DIR, // .hps_io_usb1_inst_DIR

input wire hps_io_hps_io_usb1_inst_NXT, // .hps_io_usb1_inst_NXT

input wire hps_io_hps_io_uart0_inst_RX, // .hps_io_uart0_inst_RX

output wire hps_io_hps_io_uart0_inst_TX, // .hps_io_uart0_inst_TX

output wire [14:0] memory_mem_a, // memory.mem_a

output wire [2:0] memory_mem_ba, // .mem_ba

output wire memory_mem_ck, // .mem_ck

output wire memory_mem_ck_n, // .mem_ck_n

output wire memory_mem_cke, // .mem_cke

output wire memory_mem_cs_n, // .mem_cs_n

output wire memory_mem_ras_n, // .mem_ras_n

output wire memory_mem_cas_n, // .mem_cas_n

output wire memory_mem_we_n, // .mem_we_n

output wire memory_mem_reset_n, // .mem_reset_n

inout wire [31:0] memory_mem_dq, // .mem_dq

inout wire [3:0] memory_mem_dqs, // .mem_dqs

inout wire [3:0] memory_mem_dqs_n, // .mem_dqs_n

output wire memory_mem_odt, // .mem_odt

output wire [3:0] memory_mem_dm, // .mem_dm

input wire memory_oct_rzqin, // .oct_rzqin

input wire reset_reset_n // reset.reset_n

);- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Atif,

That port is an interface of avalon-mm slave that can be used to implement read and write interfaces for master and slave components. The following are examples of components that typically include memory-mapped interfaces and in your case is avalon fifo memory.

• Microprocessors

• Memories

• UARTs

• DMAs

• Timers

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page