- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

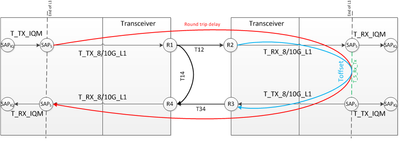

目前在使用intel的CPRI的ip,看数据手册,如果PMA环回,ip给出的round trip delay是否就是TX_EX_DELAY与RX_EX_DELAY的和呢,PMA环回后,读TX_EX_DELAY与RX_EX_DELAY与round trip delay的值,时钟周期分别是8/44/169,这里CPRI的线速是10.1376G,采用的EX_DELAY_CLK是307.2MHZ,配置的M/N为1,也就是说TX_EX_DELAY与RX_EX_DELAY与round trip delay分别为26ns/143ns/550ns,这里round trip delay多出来的这部分时延是什么呢,有寄存器可以查询到吗,使用的是A10660的片子?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The round trip delay is the sum of the Tx path delays through the REC master and the RE slave, the Rx path delays through the REC master and the RE slave, the cable delay, and the Tx-to-Rx switching delay, sometimes referred to as the loopback delay. The Tx-to-Rx switching delay is labeled T_S_Rx_Tx in the figure. The Tx-to-Rx switching delay depends on the loopback path and the device.

For the further information about the round trip delay, you may refer to link below Section 3.18.3.3, pg 115, https://www.intel.com/content/www/us/en/docs/programmable/683595/23-1-19-7-0/round-trip-delay.html

For the further information about the round trip delay register, you may download the register map file in Section 5,

https://www.intel.com/content/www/us/en/docs/programmable/683595/23-1-19-7-0/core-registers.html

Best regards,

Zi Ying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since long time no hear any feedback from you, I am now close the case.

If you have any issue after the case closed, please do feel free to submit another issue.

Best regards,

Zi Ying

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page