- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

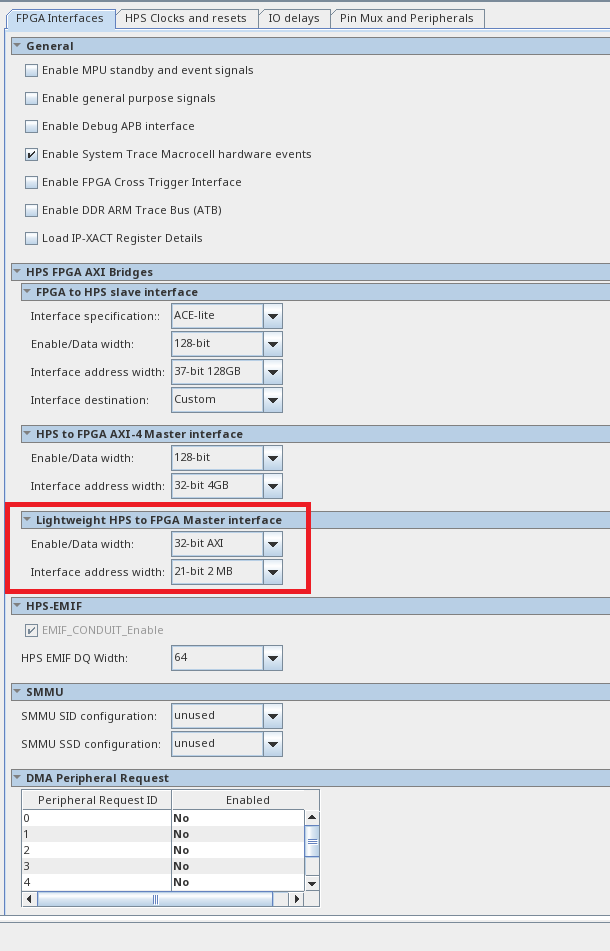

Objective: We are trying to access the FPGA fabric from the HPS region through the light weight AXI BUS.

Issue: I am not able to access the address map 0xF900_0000.

I am using the SOF from rocket board.

Uboot: uboot-socfpga from Github.

ATF: arm-trusted-firmware from Github

NOTE: All details are in the attached document.

There were few other registers that I was not able to access but, after including them in the ATF I was able to.

Even if I include the address 0xF900_0000 in the ATF, from uboot console using the command "md" or "smc", I am not able to access it.

Please find the attached document for detailed description.

What wrong am I doing and how the issue can be resolved?

Kindly help me to resolve the issue.

Best Regards,

Sanjat

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sanjat

Could you try out the "bridge" command to enable the bridge before trying to access the light weight bridge.

You could try out the command below:

bridge enable 0x2

This command will enable the light weight bridge.

You could understand more of the command by entering only the "bridge" command.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Teh,

Thanks a lot for replying and the suggestion.

I did try the above command, but, it failed.

Before loading the .RBF file, I had ran the command "bridge disable"

SOCFPGA_AGILEX # bridge disable

FPGA not ready. Bridge reset aborted!

SOCFPGA_AGILEX # fpga load 0 ${loadaddr} ${filesize}

..FPGA reconfiguration OK!

SOCFPGA_AGILEX # bridge enable 0x2

Failed to enable the HPS bridges, error 4

SOCFPGA_AGILEX #

Kindly suggest what else should I do.

Best Regards,

Sanjat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Teh,

Can you please suggest what else do I have to do inorder to verify that I am able to access the FPGA address man 0xF900_0000.

I am indeed in need of help.

Best Regards,

Sanjat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sanjat

Did you enabled the lightweight bridge in the Quartus Project?

Could you please try running out the GHRD RBF to check the bridge connection is working first?

https://www.rocketboards.org/foswiki/Documentation/AgilexSoCGSRD

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sanjat

Any update on this case?

If you are not editing it from the GSRD.

Please take note to add the declaration of the bridge in the device tree.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Teh,

Thanks for the reply.

I have done the below:

i. Modified the device tree in Uboot: socfpga_agilex7.dtsi.

I made the below modification to include the light weight AXI and normal AXI bus access:

In order to make the change, I took reference from the existing device tree implementation in Uboot.

fpga_bridge_lwsoc2fpga: lwsoc2fpgabridge@f9000000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "gdsys,ihs_axi";

reg = <0xf9000000 0x00200000>;

reg-names = "axi_h2f_lw";

clock-names = "h2f_lw_axi_clock";

resets = <&rst LWHPS2FPGA_RESET>;

little-endian;

init-val = <1>;

u-boot,dm-pre-reloc;

};

fpga_bridge_soc2fpga: soc2fpgabridge@80000000 {

#address-cells = <1>;

#size-cells = <0>;

compatible = "gdsys,ihs_axi", "simple-bus";

reg = <0x80000000 0x40000000>;

reg-names = "axi_h2f";

clock-names = "h2f_axi_clock";

resets = <&rst SOC2FPGA_RESET>;

little-endian;

init-val = <1>; //H2F_AXI_MASTER>;

u-boot,dm-pre-reloc;

};

I am able to enable the bridge using the below command:

bridge enable 0x2 as well as bridge enable 0x3

I created a new DTSI file named my_agilex_fpga.dtsi and include it in the socfpga_agilex7_socdk.dts as below:

#include "my_agilex_fpga.dtsi"

I followed the below page to create the "my_agilex_fpga.dtsi" file:

https://www.rocketboards.org/foswiki/Documentation/HOWTOCreateADevicetreeForAgilexSoC#:~:text=dtsi%20file%20contains%20the%20definition,all%20the%20HPS%20IO%20peripherals.

Kindly let me know whether I am doing things correctly or not.

Best Regards,

SpectralSensors

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Teh,

It seems my issue got resolved.

If I face any other issue then I will create another ticket.

Best Regards,

SpectralSensors

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Since this thread been resolve, I shall set this thread to close pending. If you still need further assistance, you are welcome reopen this thread within 20days or open a new thread, some one will be right with you. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

If you happened to close this thread you might receive a survey. If you think you would rank your support experience less than 10 out of 10, please allow me to correct it before closing or if the problem can’t be corrected, please let me know the cause so that I may improve your future service experience.

Regards

Jingyang, Teh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page