- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi everyone,

im using Arria 10 GX development kit.

im trying to learn EMIF example design.

im using ARRIA 10 GX development kit with DDR4 HILO preset.

memory parameters:

memory clock freq:1066.667Mhz

pll ref clk freq:133.33Mhz

after synthesis im getting the following signal status:

traffic gen pass = 0.

traffic gen fail = 1.

calibration success = 1.

i assume DDR4 calibration was successful but the test failed.

i tried to change the pll ref clk freq to the recommended(266.66Mhz)freq.

also changed the si5338 on board from 133Mhz to 266Mhz.

do you know any issue with this example design?

does it support pll ref clk of 266Mhz for this example design?

BR,

Ram.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

Thank you for submitting your question in Intel Community.

I'm Adzim, application engineer will assist you in this forum.

I would like to hear more details about the issue that you're facing right now.

Which example design that you're using currently?

- Is it generated from Quartus?

- Which Quartus version that you are using?

Since you're using Arria 10 GX Development Kit, have you checked the Development Kit with BTS program on DDR4?

"i assume DDR4 calibration was successful but the test failed."

- Yes you are right. The DDR4 calibration does passing but failed in Traffic Generator test.

"do you know any issue with this example design?"

"does it support pll ref clk of 266Mhz for this example design?"

- By right the PLL REF CLK should be able to support 266MHz and I think this is the highest setting when memory clock frequency is 1066MHz.

I can try to replicate the issue from my end when you let me know about the example design details.

You can share some snapshots of the EMIF IP setting or provide the EMIF IP in this forum.

Looking forward for your feedback. Thanks!

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Adzim,

thank you for the fast answer.

i currently generated it from EMIF IP

Im using quartus 21.1-standard.

I didn't check it with BTS.

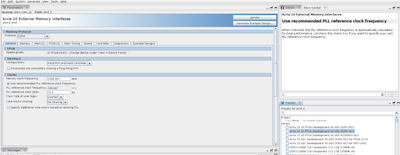

I generated the example design with the preset marked in the picture above.

then i performed synthesis with signal tap. and loaded the board.

hope you have enouth details.

BR,

Ram.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

Thank you for your feedback.

Please allow me some times to replicate the issue at my side.

I will let you know by next week.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

Sorry for keeping you waiting.

Can share your generated example design in this forum?

I don't observe similar issue at my end.

Do you able to test the board with BTS?

By right there is no error encounter during the board test run in BTS.

Just need to make sure to use similar Quartus version as the BTS and design.

Have you tried to run other example design in this board before?

Is there any other Arria 10 board at your end?

Regards,

Adzim

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

I would like know if you have any feedback to my last reply?

Or your problem has been resolved?

Do let me know if you need help in this forum.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Adzim,

sorry for the delay,

i attached the example design here for your check .

i didnt use the BTS .

I'm using quartus 21.1-standard.

we use ARRIA 10 GX development kit.

we have 2 developement kits and i checked the example design on both and it failed.

do you know if the example design support with other pll clocks values? i tried to use 266.66Mhz by configuring the clock generator on the EVB.

br,

Ram.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ram,

The example design should be able to support other clocks value.

If you are not sure about that, you can configure the EMIF IP setting with other clock value and run a compilation.

If the timing report shows that there is no issue with DDR timing, then the design should be okay.

I can suggest to run a DDR4 test with BTS application.

Also can you use latest Quartus release to run the test?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous reply that we have provided, I now transition this thread to community support. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page