- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

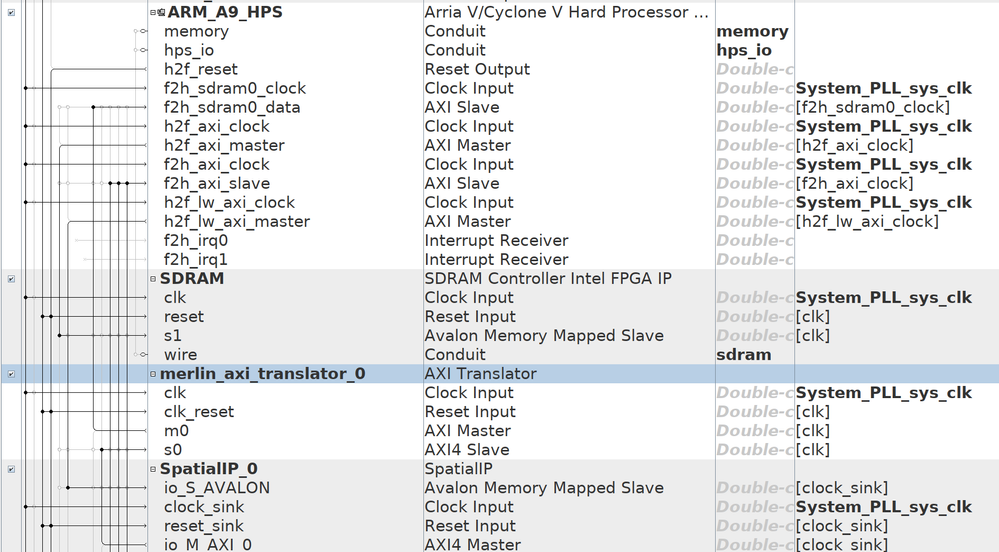

I'm trying to share read and write access to the SDRAM between HPS and FPGA of a DE1SoC Dev board (Cyclone 5). Attached is the system I created in Platform Designer 19.1. Basically, I have an AXI4 from SpatialIP (an IP I created) connected to an AXI4 Master to AXI3 translator, and then to the fpga_sdram bridge on the HPS. After testing on the board, I find that BVALID never asserts even though I asserted WVALID, WREADY and WLAST for 1 cycle from the AXI Master, and BREADY is always high. On Cyclone V, what would cause the DRAM controller to not assert BVALID? Do I need to do any extra setups in order to enable the fpga2sdram connection? Am I missing anything here?

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I figured it out myself. It seems to be the case that on DE1SoC, when u-booting, one needs to enable the fpga2sdram_handoff and bridge_enable_handoff in order instruct the HPS to enable SDRAM bridge connections. I'm not sure if this is documented anywhere in the qsys / quartus manuals.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We recommend that you check out rocketboards.org (and select "START") for recommended booting steps and for this case, a u-boot script usually handles the bridge enables, you may refer here on how to get the u-boot script:

https://rocketboards.org/foswiki/Documentation/AVGSRDSdCard

You may also refer to:

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/embedded/2016/how-and-when-can-i-enable-the-fpga2sdram-bridge-on-cyclone-v-soc.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any follow up from your side?

Best Regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page