- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm aware that DIFFCLK pins can be used as general I/O, however can a single ended clock be used on one of the pins, with general I/O used on its differential pair?

I am using a Cyclone 10 LP if that makes any difference.

Cheers!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I forgot to also mention these are CLK#/DIFFCLK_# input pins. Not output or I/O.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi yes2,

No.

The (p) and (n) pins of a differential pair is fix. For example, in Quartus, when you set the (p)'s pin location of a differential signal, the n-terminal will be set accordingly.

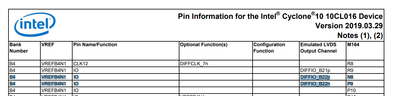

You can also see this from the device Pin Information document. Example as below.

Best Regards,

Xiaoyan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, previous post dosn't seem to answer your specific question.

I unerstand that you want to use CLK pins with single ended clock signal. In this case, p and n pin of a pin pair are independent. You can e.g. use CLK0 (DIFFCLK_0p) as clock input and CLK1 (DIFFCLK_0n) as user input signal.

Generally, refer to current pin connection guideline https://www.intel.com/content/www/us/en/docs/programmable/683137/current.html

and test the chosen pin configuration in Quartus.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since you didn't give further comments, I wonder if you have got the answer for the question?

If you still have more questions related, please feel free to ask here!

If no, we will close this case. Thanks!

Best Regards,

XY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page