- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

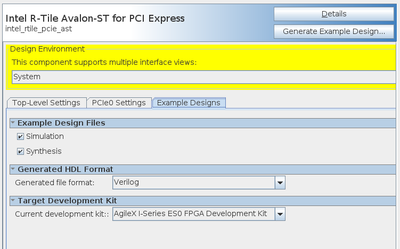

I've been trying to compile a PCI Express example design for the Agilex I-series devkit.

1. Nothing works on the projects provided here ES (21.2 or higher)

Found here: https://www.intel.com/content/www/us/en/products/details/fpga/development-kits/agilex/i-series.html

Programming the sof present in the zip using Quartus Pro 21.2, rebooting the server, board not detected by lspci

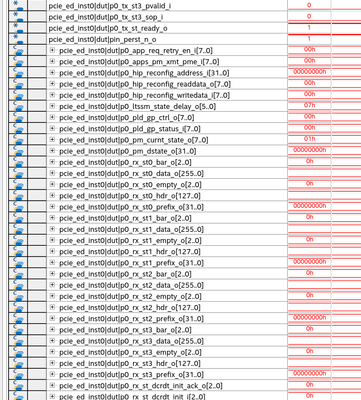

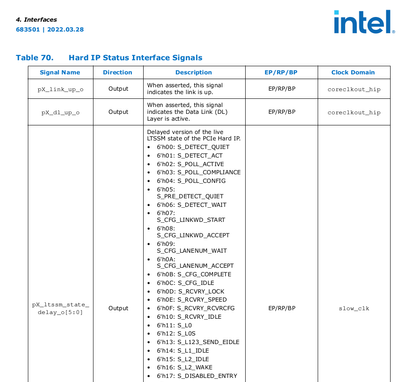

pcie_ed_inst0|dut|p0_ltssm_state_delay_o[5..0] seems to be stuck to 0x07=S_CFG_LINKWD_START

The motherboard has no issues with any other PCIe cards.

2. Using Quartus Pro 22.1, I followed UG-20330 to generate from scratch the example design.

The compilation ends successfully but the board isn't detected either.

Could you please provide a working example design for the intel devkit already compiled to be sure the problem isn't on the project?

Also what is S_CFG_LINKWD_START?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the issue.

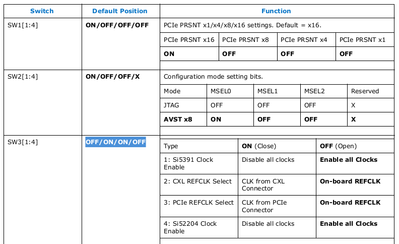

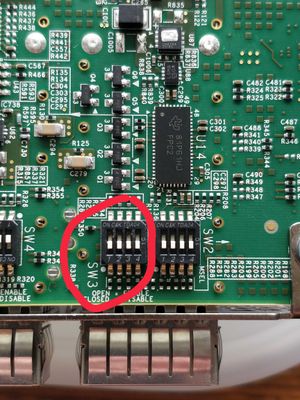

The default position for the SW3 is defined in the UG as OFF/ON/ON/OFF, to use the refclk from the connector.

The board was received with OFF/OFF/OFF/OFF, to use the on-board refclk.

I set the SW3 as documented and it's now enumerated by the bios and seen in lspci.

Why it doesn't work using the on-board refclks?

Devkit: DK-DEV-AGI027RES

Serial number: AGIPCIE8000248

Regards,

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for reaching out.

Just to let you know that Intel has received your support request and I am assigned to work on it.

Allow me some time to look into your issue. I shall come back to you with the findings.

Thank you for your patience.

Best regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Wincent_Altera,

Thank you for your help, we are completely blocked due to this issue and have no way to debug it by ourselves.

Please let me know if you need anything more.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Wincent_Altera,

Thank you, it's currently compiling with Quartus Pro 21.2.

At this moment, I don't have a Gen4x16 capable motherboard available, only Gen3x16.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Initially, I suspend R-Tile's different behavior on different Motherboard may be related to Preset negotiation between Motherboard and R-Tile.

Is okay, let see the result after you compile the file.

Looking forward to hear back from you.

Regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

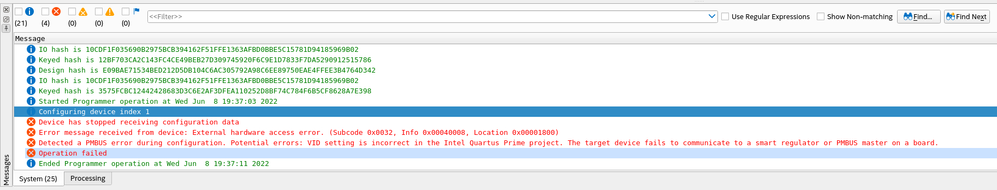

It compiled successfully but the Programmer fails at 5%:

Error(18950): Device has stopped receiving configuration data

Error(18948): Error message received from device: External hardware access error. (Subcode 0x0032, Info 0x00040008, Location 0x00001800)

Error(22248): Detected a PMBUS error during configuration. Potential errors: VID setting is incorrect in the Intel Quartus Prime project. The target device fails to communicate to a smart regulator or PMBUS master on a board.

Error(209012): Operation failed

Just in case, I attached the archive of the example design (2. in my question) generated with 22.1.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The example work fine in our server, in this case error might happen on the settings.

- Can you please, remove the card from the PCIe slot. Make sure the PCIe edge connector and the slot are clean. Try re-inserting and ensure the card is fully seated in the PCIe slot.

- Have you rebooted Linux after loading the .sof?

- For the Error (22248): Can you please check if the VID setting is appropriate ?

You may refer the guide : https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/agilex/ug-ag-pwr.pdf#pag... - If not workable, Can you please try out other Agilex Design Example and see is it the error still the same ?

https://www.intel.com/content/www/us/en/support/programmable/support-resources/design-examples/design-store.html?s=Newest&f:guidetm83741EA404664A899395C861EDA3D38B=%5BIntel%C2%AE%20Agilex%E2%84%A2%20FPGAs%20and%20SoC%20FPGAs%5D

Looking forward to hear back from you. Please let me know if any other further clarification is needed.

Regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I receive a new update on R-tile bug issue, it might be one of the root causes of your problem.

Please refer the link below, download and install the patch, the problem shall fixed in future release

https://www.intel.com/content/www/us/en/support/programmable/articles/000090874.html

Let me know if this help, Looking forward to hear back from you

Regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Wincent_Altera,

- I added the smartVID to your project and it programs successfully now.

- I tried 3 different motherboards (up to Gen3x16) and no one detects the card with the 22.1 project and your project.

- I checked several times the physical connection, no issues, it's fully in and it works with all the other PCIe cards we have. Nevertheless, I could only test in lab servers where the card is vertically plugged in due to the PCIe bracket being 1cm taller than the standard size.

Thank you for the patch, I installed it and the project is compiling.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the issue.

The default position for the SW3 is defined in the UG as OFF/ON/ON/OFF, to use the refclk from the connector.

The board was received with OFF/OFF/OFF/OFF, to use the on-board refclk.

I set the SW3 as documented and it's now enumerated by the bios and seen in lspci.

Why it doesn't work using the on-board refclks?

Devkit: DK-DEV-AGI027RES

Serial number: AGIPCIE8000248

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Glad that you solve the issue, thanks for sharing with me as well

Seen that the problem happens on the refclks settings if follow Error Code 18948

https://www.intel.com/content/www/us/en/support/programmable/articles/000086828.html

With that, I am setting this case to close status at this time.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread. Thank you

I would appreciate taking a moment to fill out the short survey with regards to your experience using Intel Forum.

Regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Before closing the issue, I would like to understand why it doesn't work setting the on-board refclk in SW3.

There is something wrong somewhere, I don't get the Error Code 18948 with the example design since the board is successfully programmed and I can use SignalTap to see the internal signals (cf. the screenshot in the question). However, the board wasn't enumerated.

Is that a hardware issue of the devkit?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

No worries, I will remain this case open.

As my understand from your previous reply, you mention that

"the device is enumerated after you set the SW3 as documented, and seen in lscpci. "

As per mention, my understanding is it works as usual already, can I know why suddenly it cannot be enumerate?

Can you clarify more?

Regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm just curious of the reason since it is supposed to work out of the box with both switch positions.

Using the same sof file, SW3[3] (PCIe refclk selection) set to:

| OFF=On-board refclk | Not working (hence my question); Programming OK but enumeration not working |

| ON=CLK from PCIe Connector | Working |

Why using the on-board refclk doesn't work? Is it a hardware issue? Maybe the clocks aren't populated in the PCB for this ES devkit?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I wish to clarify your question,

But that is related to hardware design. Unfortunately, our team has no visibility on it.

Let me know if you have any further question.

Regards,

Wincent_C_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Understood, thank you for your help.

Regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page