- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

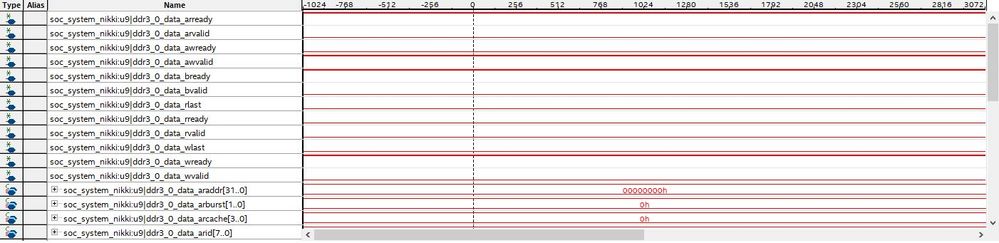

While using Avalon MM , I can write and read from ddr3. I want to use AXI3 instead of Avalon MM . I rebuild the soc_system with FPGA-to-HPS SDRAM Interface- AXI3(128 bit data). While anaylsing the waveform, axi_awready is always low in both idle case and write operation. Is there any example soc design using AXI3 interface ?

Regards,

Nithin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NKRIS7,

I am sorry for the delay in response as I had to attend company's meeting yesterday. I truly apologize for the delay.

The waitrequest is a mechanism for throttling the source of traffic to the IO Slave port. If the waitrequest is asserted High (or in other word axi_awready is always low) , it means the IO slave port does not have enough resources to keep accepting the write burst. It requests some time to wait for data processing. So, may I know for how long is the waitrequest remain high ? Is it too long ?

By the way, I found a project on RocketBoards utilizing FPGA2SDRAM interfaces:

https://rocketboards.org/foswiki/Projects/CycleVSoCSDRAMPerformanceExampleDesign

Perhaps you can take a look on that. 😊

Also you may want to read through this KDB solution and check if any setting miss out :

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/embedded/2016/how-and-when-can-i-enable-the-fpga2sdram-bridge-on-cyclone-v-soc.html

Thanks

Regards,

NAli1

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NKRIS7,

There are several example and demo related to AXI interface as per listed below. Hopefully this is helpful for you. If not,please don’t hesitate to ask for more details.😊

1) BFM Simulation Example: HPS AXI* Bridge Interface to FPGA Core:-

The Hard Processor System (HPS) in Intel SoC devices has a HPS-to-FPGA AXI* Bridge (h2f) interface for communicating with memories and peripherals in the FPGA core.

https://www.intel.com/content/www/us/en/programmable/support/support-resources/design-examples/design-software/qsys/exm-hps-axi-bfm.html

2) Demo AXI Memory Design Example:-

This design example demonstrates an AMBA* AXI*-3 slave interface on a simple Verilog custom memory component for Qsys systems. You can use this example as a basis for your own custom AXI slave interfaces.

https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/design-examples/design-software/qsys/exm-demo-axi3-memory.html

3) Designing with AXI for Altera SoC ARM Devices Workshop Lab - Instantiating Your AXI3 Component:-

https://fpgawiki.intel.com/wiki/Designing_with_AXI_for_Altera_SoC_ARM_Devices_Workshop_Lab_-_Instantiating_Your_AXI3_Component

Also, you may refer to this handbook to get details on the design guideline for Cyclone® V SoC FPGAs and Arria® V SoC FPGA.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an-cv-av-soc-ddg.pdf

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NAli1,

Thank you for your reply.

I am working on FPGA2SDRAM interface. I am using the demonstration file (DDR3_RTL) given in CD of DE10-nano. In that terasic_hps_ddr3.img is used as uboot. I changed FPGA2SDRAM interface to axi interface (originally Avalon MM ). As per reference manual axi need 2 command port for read and write. axi read is in command port 0 and it works fine. But axi write is in command port 1 and axi_awready is always low.

While checking u-boot bootcmd

fpga2sdram_handoff = 0x000001ff. which means only port 0 is active and others are in reset condition. I change fpga2sdram_handoff to 0x000003ff . but still ready is axi_awready is always low.

Is it right way to do fpga2sdram interface ?

Regards,

Nithin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi ,

I see that all the columns you sent are looped on HPS, so where is the data stream generated

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NKRIS7,

I am sorry for the delay in response as I had to attend company's meeting yesterday. I truly apologize for the delay.

The waitrequest is a mechanism for throttling the source of traffic to the IO Slave port. If the waitrequest is asserted High (or in other word axi_awready is always low) , it means the IO slave port does not have enough resources to keep accepting the write burst. It requests some time to wait for data processing. So, may I know for how long is the waitrequest remain high ? Is it too long ?

By the way, I found a project on RocketBoards utilizing FPGA2SDRAM interfaces:

https://rocketboards.org/foswiki/Projects/CycleVSoCSDRAMPerformanceExampleDesign

Perhaps you can take a look on that. 😊

Also you may want to read through this KDB solution and check if any setting miss out :

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/embedded/2016/how-and-when-can-i-enable-the-fpga2sdram-bridge-on-cyclone-v-soc.html

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai Nali1,

Thank you so much for your assistance . Finally It worked😃 . The second link you have mentioned solved the problem.

Regards,

NKRIS7

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Glad to know its working now. You are more than welcome .😊

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page