- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i wanna Communicate Logic <-> Nios using Avalon MM Pipeline slave..

is there any Examples?

Nios(Qsys, Avalon MM Pipeline Slave) <-> Logic

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jongyun ,

I'm Eliath and I'll help you with this, I just have a few questions:

does your design have a component on Qsys? or it is only code?

Is VHDL or Verilog the language you are using for the logic?

Which Quartus version are you using?

Regards,

-Eliath

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In my design, NIOS is my master.

Quartus 17.1 // Qsys(Platform Designer)

1. Nios

1.1 Onchip-memory

1.2 jtag

1.3 Avalon -MM-Pipelined-Slave (conduit to Logic)

* Address, Wr_n/Rd_n / ReadData / WriteData / WaitReq / ReadVaild

i wanna communicate with Vhdl/Verilog Logic .

Nios <-> Logic

===============================================

Main Clock : 50Mhz (Logic, Nios)

Befored i using without pipelined Options (* ReadVaild, WaitReq)

--- Without Using (* ReadVaild, WaitReq)

proess(RD_n, Address)

begin

if RD_n = '0' -- Nios wanna Read Data

case Address(15 downto 0) is

when x"0000" => ReadData <= x"00000000";

....

...

when others => ReadData <= x"ffffffff";

end case

else

ReadData <= (others => 'z');

end if;

end process;

=================

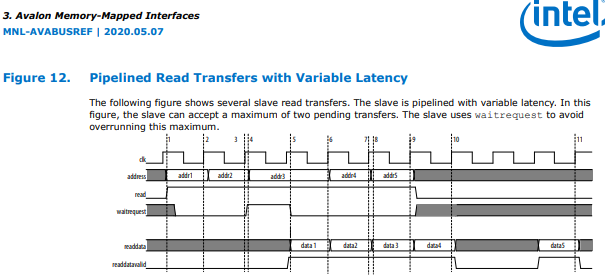

i'm not sure what is mean "Maximum pending read Transactions"

* IF i Set Maximum Pending Read Transactions = 2 then,

* 1.1 At Slave sides, Read 2 Addr1, Addr2 (When Rising Clock) (Refer Below Timing Diagram)

* 1.2 After Read 2 Times Slave Asset WaitReq to High

* 1.3 Wait a Clock Delay (Sync to Where? need to make Another Clock?)

* IF i Set Maximum Pending Read Transactions = 4 then,

* 2.1 At Slave sides, Read 4 [Addr1, Addr2, Addr3 ,Addr4] When Rising Clock

* 2.2 After Read 4 Times Slave Asset WaitReq to High

* 2.3 Wait a Clock Delay (Sync to Where? need to make Another Clock?)

refer : https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_avalon_spec.pdf

Page #. 29

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jongyun,

it is not needed to implement one more clock due to the following:

- New .qsys files include Clock Source component ( clock aggregator)

- When connecting two interfaces:

- Clock input interface fed from the outside system (is exported out of the system, by default)

- Clock Output interface connects to Clock Input Interfaces of other system components.

- Clock column will help to have a quick clock signal connection.

I'd like to share an example design for Avalon Memory-Mapped Slave

in the link, after table one you will find two useful links.

Please let me know how useful the information was to solve the issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jongyun,

Hoping you're well I was wondering if the information I shared with you was helpful and if there's something more I could help you with.

Regards,

-Eliath

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page