- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) unknown commands: 0x3F2, 0x3F4, 0x307, 0x002, 0x004, 0x03E

Unknown addresses: 0x480008,0x500008,0x6C48A50F

2) Using JAM STAPL Player downloaded from Intel website, without changing any timing parameter, reading ID is failed, i.e. TDO flat. When a manual reading executed (Write CMD0x06 (IDCODE)) and read the ID immediately, i.e. no 5 us idle delay by default in the JAM player code, the ID showed up from TDO bus. The questions are

1) Does the default idle delay parameter in the source code need to modified based on FPGA and Processor speed ( we saw the description in some documents)?

2) If so, Is any reference of timing model related to MAX 10 FPGA and processor speed model or parameter available?

3) All read commands have same delay?

4) What do we need pay attention to write command or erase command?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Forgot to mention that I try to use JAM STAPL player (downloaded from Intel website) implemented to on board processor to configure MAX 10 FPGA.

From the downloaded code, we found some commands and addresses used but no definition could be found. These commands and addresses were listed above.

With downloaded code, we can't get reading ID through (command 0x06 ID_CODE). The TDO bus is flat. However, when we manually sending the command. The ID code is obtained. The only difference is the JAM STAPL Player code has default 5 us delay, the manual command does not. Now I have question about the delay

1) Does the default idle delay parameter in the source code need to modified based on FPGA and Processor speed ( we saw the description in some documents)?

2) If so, Is any reference of timing model related to MAX 10 FPGA and processor speed model or parameter available?

3) All read commands have same delay?

4) What do we need pay attention to write command or erase command?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi TLu4,

Actually there is some issue with JAM STAPL player (quatur_jli command-line executable).

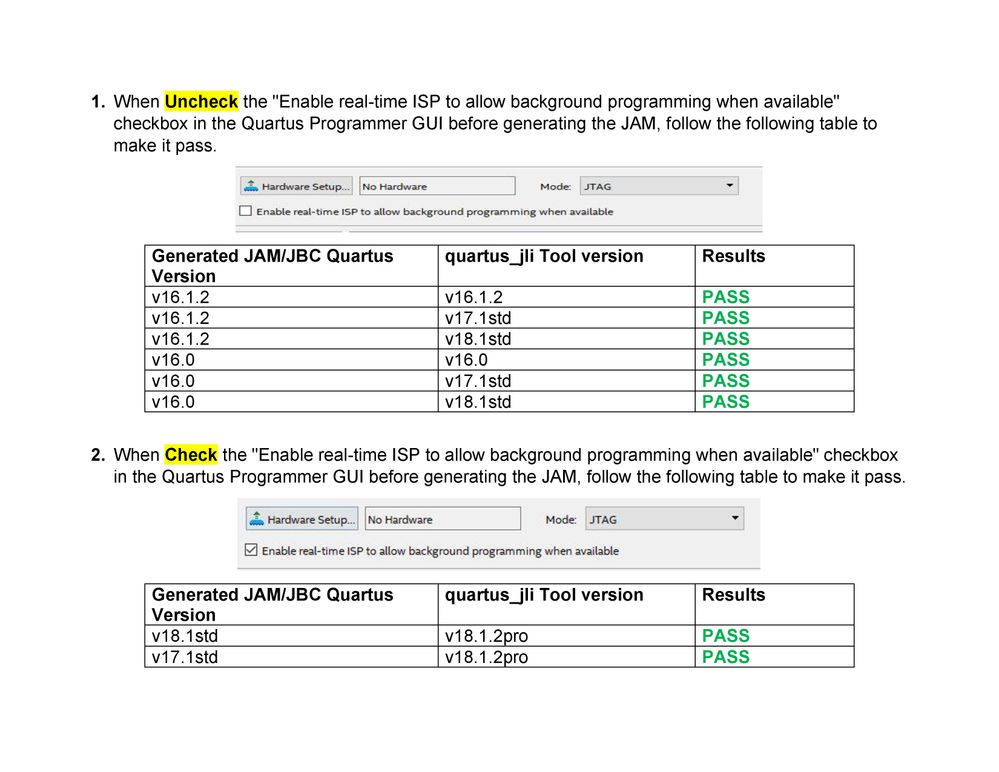

If you refer picture above, only certain Quartus and JAM STAPL player version combination is pass (pass means able to program without failure).

For example:

- You not using real-time ISP (Uncheck), you are using Quartus 16.0 version to generate JAM/JBC. And you are using JAM STAPL player 16.0 version. Thus, the results is pass (able to program without failure).

- You not using real-time ISP (Uncheck), you are using Quartus 18.1 version to generate JAM/JBC. And you are using JAM STAPL player 16.0 version. Thus, the results is failed/error (this Quartus and JAM STAPL player version combination did not have in above picture).

In conclusion, only version combination in picture above able to program in JAM STAPL player successfully.

I hope this will help.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Shafiq.

Is there any updated STAPL player matching Quartus version?

We managed using .jbc and Byte-code player. It works. Why is that?

Thanks.

Tim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shafiq,

Some background.

1) I am using Quartus 18.1 std version generating the .jam and .jbc.

2) We downloaded JAM STAPL player code and ported to a processor. The purpose is the FPGA can be remote updated .

3) Enable Real Time ISP is unchecked.

Thanks.

Tim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi TLu4,

As for now, there no updated STAPL player matching latest Quartus version.

It might be work, but sometime the verify take longer time, examine take longer time and etc.

The one the perfectly work are from table above (have been tested from Engineer and internal folks).

I hope this clear.

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page