- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

module alarmsystem(clr,clk,alarm,CT,WT,Display);

input clk,clr;

input [31:0]CT;

input [31:0]WT;

output alarm;

output [31:0]Display;

wire reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5;

wire reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5;

wire S;

Temp_controller

Temp_controller_1(reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5,reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5,S,alarm,clr,clk);

Temp_datapath

Temp_datapath_1(reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5,reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5,clk,S,CT,WT,Display);

endmodule

module Reg_32(I,Q,clk,clr,ld);

input[31:0]I;

input clk,clr,ld;

output [31:0] Q;

reg[31:0]Q;

always@(posedge clk)

begin

if (clr)

Q<=32'b00000000000000000000000000000000;

else if (ld)

Q<=I;

else

Q<=Q;

end

endmodule

module Add_32(X,Y,Z);

input[31:0]X,Y;

output[31:0]Z;

assign Z=X+Y;

endmodule

module Shift_32(I,Z);

input[31:0]I;

output[31:0]Z;

assign Z=(I>>2);

endmodule

module Comp_32(X,Y,Z);

input[31:0]X,Y;

output Z;

reg Z;

always@(X or Y)

begin

//////Z<=0;

if(X<Y)

Z<=0;

else

Z<=1;

end

endmodule

module Temp_datapath(reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5,reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5,clk,S,CT,WT,Display);

input clk,reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5,reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5;

input [31:0]CT,WT;

output[31:0]Display;

output S;

wire[31:0]wire_1,wire_2,wire_3,wire_4,wire_5,wire_6,wire_7,wire_8;

Reg_32 reg1(CT,wire_1,clk,reg_clr1,reg_ld1);

Reg_32 reg2(wire_1,wire_2,clk,reg_clr2,reg_ld2);

Reg_32 reg3(wire_2,wire_3,clk,reg_clr3,reg_ld3);

Reg_32 reg4(wire_3,wire_4,clk,reg_clr4,reg_ld4);

Reg_32 reg5(h,Display,clk,reg_clr5,reg_ld5);

Add_32 add1(wire_1,wire_2,wire_5);

Add_32 add2(wire_3,wire_4,wire_6);

Add_32 add3(wire_5,wire_6,wire_7);

Shift_32 shift1(wire_7,wire_8);

Comp_32 shift2(Display,WT,S);

endmodule

module Temp_controller(reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5,reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5,S,alarm,clr,clk);

input clk,clr,S;

output reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5;

output reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5;

output alarm;

reg reg_ld1,reg_ld2,reg_ld3,reg_ld4,reg_ld5;

reg reg_clr1,reg_clr2,reg_clr3,reg_clr4,reg_clr5;

reg alarm;

parameter S0=4'b0000,S1=4'b0001,S2=4'b0010,S3=4'b0011,S4=4'b0100,S5=4'b0101,S6=4'b0110,S7=4'b0111,S8=4'b1000;

reg[4:0] currentstate;

reg[4:0] nextstate;

always@(posedge clk ) begin

if (clr ==1)

currentstate = S0;

else currentstate=nextstate;

end

//begin

//currentstate<=nextstate;

//end

always@(currentstate or S)

begin

alarm<=0;

reg_ld1<=0;

reg_ld2<=0;

reg_ld3<=0;

reg_ld4<=0;

reg_ld5<=0;

reg_clr1<=0;

reg_clr2<=0;

reg_clr3<=0;

reg_clr4<=0;

reg_clr5<=0;

case(currentstate)

S0:begin

nextstate<=S1;

end

S1:begin

nextstate<=S2;

end

S2:begin

nextstate<=S3;

end

S3:begin

nextstate<=S4;

end

S4:begin

nextstate<=S5;

end

S5:begin

reg_ld1<=1;

reg_ld2<=1;

reg_ld3<=1;

reg_ld4<=1;

reg_ld5<=1;

if(clr==1)

nextstate<=S0;

else if(S==1)

nextstate<=S6;

else

nextstate<=S7;

end

S6:begin

alarm<=1;

if(clr==1)

nextstate<=currentstate;

else

nextstate<=S8;

end

S7:begin

alarm<=0;

if(clr==1)

nextstate<=currentstate;

else

nextstate<=S8;

end

S8:begin

reg_clr1<=1;

reg_clr2<=1;

reg_clr3<=1;

reg_clr4<=1;

reg_clr5<=1;

nextstate<=S0;

end

endcase

end

endmodule

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Use the RTL design process to create an alarm system that sets a single-bit output alarm to 1 when the average temperature of four consecutive samples meets or exceeds a user-defined threshold value (set your own threshold). A 32-bit unsigned input CT indicates the current temperature, and a 32-bit unsigned input WT indicates the warning threshold. Samples should be taken every 5 clock cycles. A single-bit input clr when 1 disables the alarm and the sampling process. Start by capturing the desired system behaviour as an HLSM, and then convert to a controller/datapath. Write your Verilog code and download your program into FPGA. Set LED as your alarm indicator.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i had a problem that my load input not connected to reg_ld...can u help me? 0166801697 this is my phone number.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sisa,

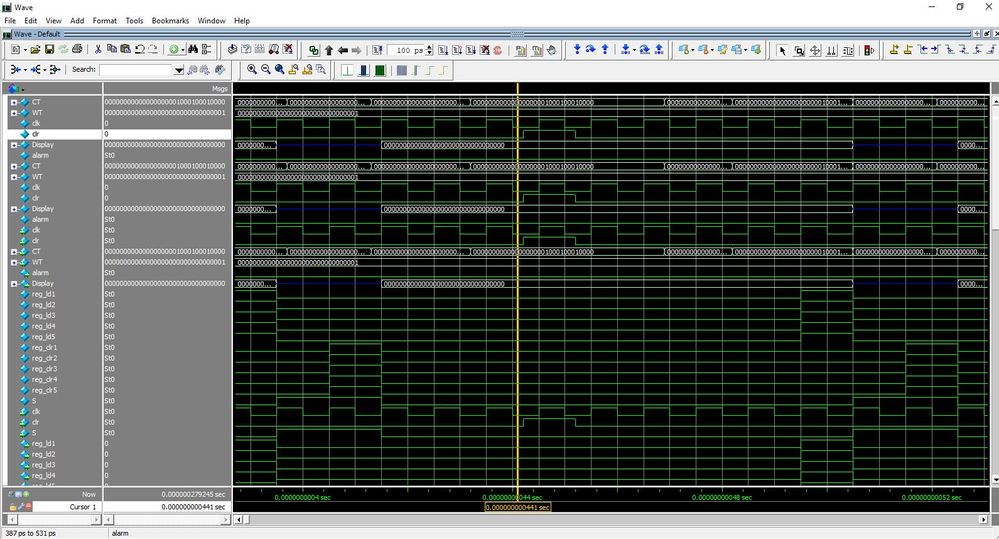

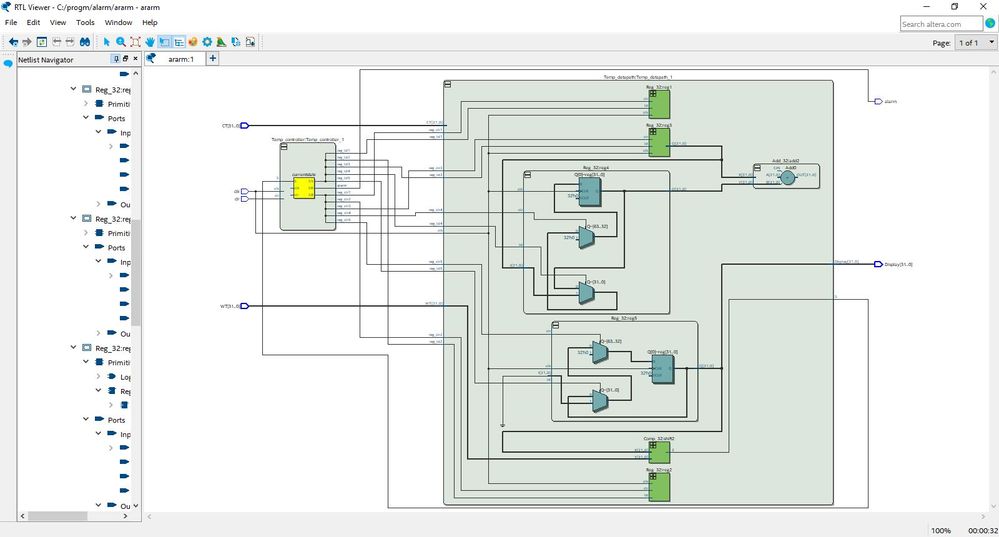

I could able to compile & simulate the design provided over here.

please find the attachments for schematic & simulation results.

Try to compile & simulate at your end & provide specific error/issue if you have.

Regards,

Vikas Jathar

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page