Cyclone V ALTLVDS Design Example

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Community

- Intel Community Knowledge Base

- Product Support Forums Knowledge Base

- FPGA Knowledge Base

- FPGA Wiki

- Cyclone V ALTLVDS Design Example

Cyclone V ALTLVDS Design Example

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Cyclone V ALTLVDS Design Example using Qsys Avalon Data Pattern Generator and Avalon Data Pattern Checker

Description

This wiki page is dedicated to users who would like an example of using:

- Cyclone V

- TerasIC Cyclone V GX Starter Development Board

- ALTLVDS_TX IP

- ALTLVDS_RX IP

- ALTLVDS_RX bit slip operation

- Qsys

- Avalon Data Pattern Generator

- Avalon Data Pattern Checker

- Manual Phase Alignment (Dynamic Phase Alignment, DPA, is not supported in Cyclone V)

- System Console

- Tcl scripting

Design Example

The following qar file contains the design example.

altlvds-c5-serial-link-prbs-qsys.qar

The example runs at 625Mb/s but has been run at 800Mb/s without error.

Hardware Used

This example runs on the TerasIC Cyclone V GX Starter board.

TerasIC Cyclone V-GX Starter Kit

Hardware Setup

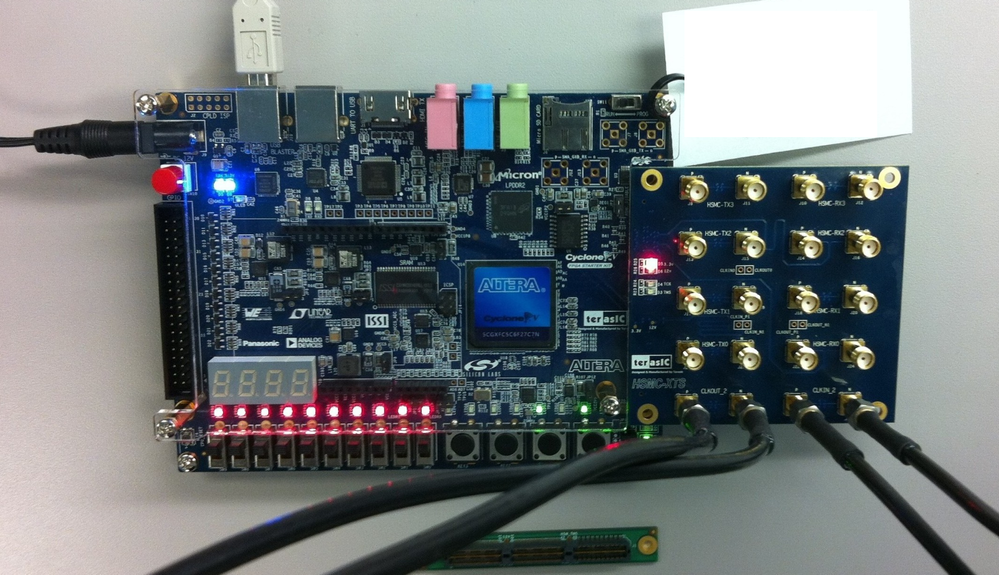

Here is a picture of the setup:

Notice in the bottom of the picture an HSMC loopback board. Initial testing was performed using the HSMC loopback connector.

The board plugged into the TerasIC Cyclone V GX Starter board is a TerasIC HSMC XTS daughter board and uses SMA loopback cables.

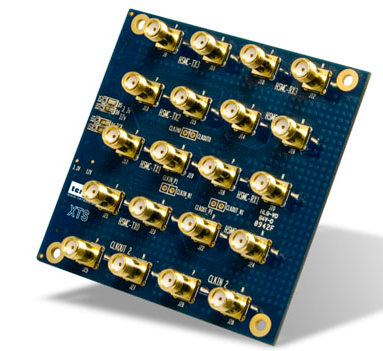

TerasIC HSMC XTS Daughter Board

Design Description

After downloading the design example and opening in Quartus, review the top level of the hierarchy, altlvds_C5_serial_link.v. This file contains instantiations for:

- Qsys

- TX PLL

- RX PLL with phase adjustment capability

- cyclonev_pll_lvds_ouptut atom

There are links to documentation in the top level code to assist in understanding.

In addition, there is miscellaneous logic for the following:

- Switch and key debounce

- Counters

- Basic count pattern generation and checking for debug of bit and word alignment

- Convert 40 bit streaming Avalon interface to 10-bit ALTLVDS TX and RX interfaces

Again, there are comments in the top level RTL that describe how to use the switches and keys on the TerasIC Cyclone V GX Starter board as well as the control register in the Qsys design.

Qsys Avalon Data Pattern Generator and Data Pattern Checker

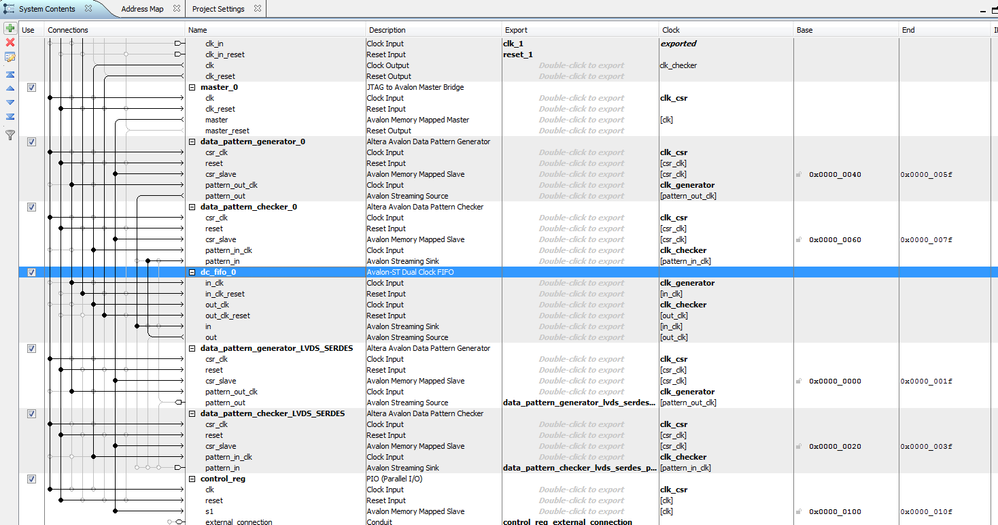

The following is a picture of the Qsys design used for this example. The design name is pattern_gen_check.qsys.

Notice that the Qsys design contains two data pattern generators and checkers. The *_0 generator and checker have a FIFO in between and were used to understand the register mapping for each. The System Console commands used are based on the memory maps of both the generator and checker (with address offset shown in Qsys).

Link to the embedded IP User's guide. Refer to page 34-5. "Avalon Streaming Data Pattern Generator and Checker Cores -> Register Maps"

Altera Embedded IP Users Guide

The second set of pattern generators and checkers (*_LVDS_SERDES) are used to send and receive data to/from the ALTLVDS_TX and ALTLVDS_RX IP blocks instantiated at the top level of the project, altlvds_C5_serial_link.v. The Avalon streaming interfaces on the data pattern generator and checker were exported to the Qsys design port map, the top level of pattern_gen_check.qsys.

The top level project file, altlvds_C5_serial_link.v, instantiates pattern_gen_check.v that was generated from Qsys. The top level project, altlvds_C5_serial_link.v, contains basic logic to allow interface to the Avalon Streaming ports that were exported in Qsys to the top level.

The Avalon streaming interface for the data pattern generator and checker is 40 bits wide. The width is converted to 10-bits for the ALTLVDS TX and RX IP at the top level, altlvds_C5_serial_link.v.

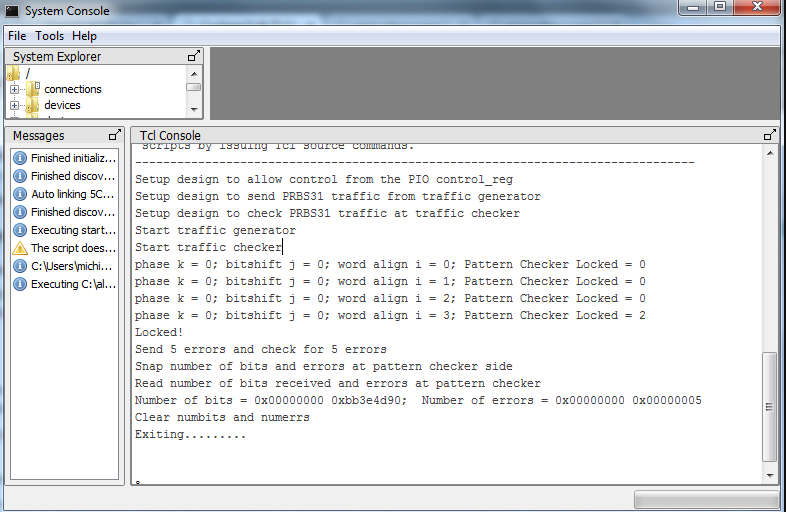

After downloading the sof file to the TerasIC board, System Console can be used to read status of the data pattern checker to determine if it can lock onto the pattern. Status can also be read to look at errors. The data pattern generator can be used to insert errors in the TX path. The System Console and Tcl Script sections of this wiki page has examples that show how to write and read the control and status of the data pattern generator and receiver.

System Console

The following file contains the System Console commands that can be used to drive the design after opening System Console.

9/96/System_Console_Pattern_GenCheck.txt

Tcl Scripts

The following Tcl script was used to automatically word and bit align the RX LVDS SERDES so that the data pattern checker can line up with the data pattern generator. Documentation links are contained in the Tcl file to assist in understanding Cyclone V fPLLs and manual phase alignment. The Tcl script also contains comments to document Qsys registers used in the example design, ltlvds_C5_serial_link.v, which instantiates Qsys design, pattern_gen_check.qsys.

The Tcl script has three loops. One to perform phase shifting, one for bit shifting, and one for word shifting. The script shifts through each and checks the data pattern checker until it is locked to a PRBS31 pattern. Once locked, the script will inject 5 errors from the data pattern generator and then check for the 5 errors in the data pattern checker status registers.

a/a8/Phase_word_and_bit_align.tcl

The following Tcl script can be used to watch the phase change occurring on pll_rx when making phase adjustments. A user can monitor the 62.5Mhz clock from pll1 and from pll_rx. Both have been brought out to JP9 on the TerasIC Cyclone V GX starter kit. While monitoring both 62.5Mhz clock outputs and running the below script, a user will see the pll_rx 62.5Mhz clock slide 360 degrees compared to the 62.5Mhz clock from pll1. Notice also that the script is checking to see if the data pattern checker stays in sync. You will see that the data pattern checker will lose and re-gain sync as the phase is incrementally offset.

Community support is provided Monday to Friday. Other contact methods are available here.

Intel does not verify all solutions, including but not limited to any file transfers that may appear in this community. Accordingly, Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

For more complete information about compiler optimizations, see our Optimization Notice.